#### Graduate Institute of Electronics Engineering, NTU

2024 Crash Course Media IC & System Lab

# From Low Power Fundamentals to SOC Low Power Design

Ke-Han Li

Graduate Institute of Electronic Engineering

National Taiwan University

2024/08/13

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

# **Motivation**

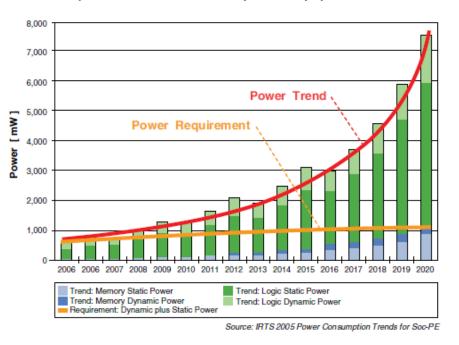

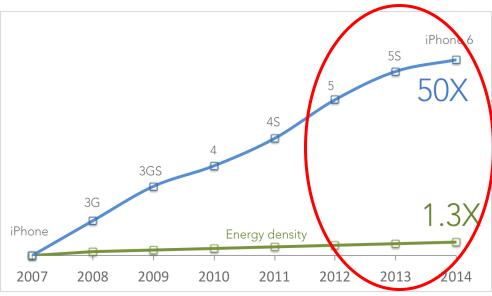

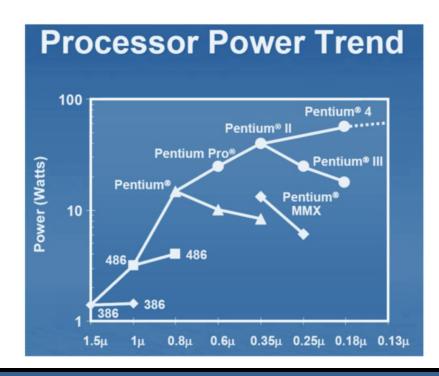

#### CHIP's power increases year by year.

# Battery capacity increases slowly due to physical limitations.

The gap is gradually widening!!!

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

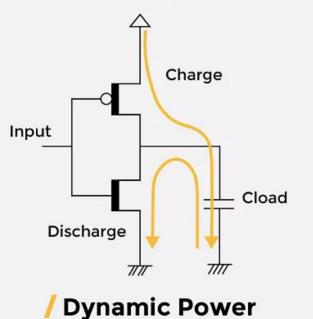

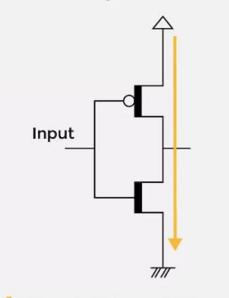

# **Power Components and Equation**

$$P_{Total} = \alpha f C_L V_{DD}^2 + t_{sc} V_{DD} I_{peak} + V_{DD} I_{leakage}$$

$\alpha = \text{activity factor (0 to 1)}$ f = frequency $t_{c}$  = transition time  $C_{i}$  = capacitive load  $V_{pp} = \text{supply voltage}$  $I_{leakage} = leakage current$  $I_{peak} = peak current$

#### Input switching to '1' or '0'

#### V<Input<VDD-1

**Short Circuit Current**

#### Input: '1' or '0' steady state

Leakage Current

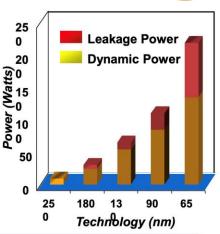

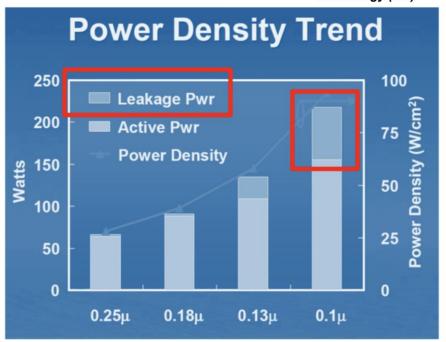

# **Leakage Power Trend**

Leakage power gradually dominates the total power in advanced technology.

# **How to Reduce Power?**

$$P_{Total} = \alpha f C_L V_{DD}^2 + t_{sc} V_{DD} I_{peak} + V_{DD} I_{leakage}$$

#### Dynamic Power

- Reduce Area(C\_L)

- Slow clock & Turn off Clock(f)

- Reduce Voltage(VDD)

- Reduce Switching Activity(α)

#### Static Power

- OFF Power(VDD)

- Reduce Voltage(VDD)

- Increase Vt(I\_leak)

$\alpha = \text{activity factor (0 to 1)}$

f = frequency

$t_{sc}$  = transition time

$C_{i}$  = capacitive load

$V_{DD} = \text{supply voltage}$

$I_{leakage} = leakage current$

$I_{peak} = peak current$

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

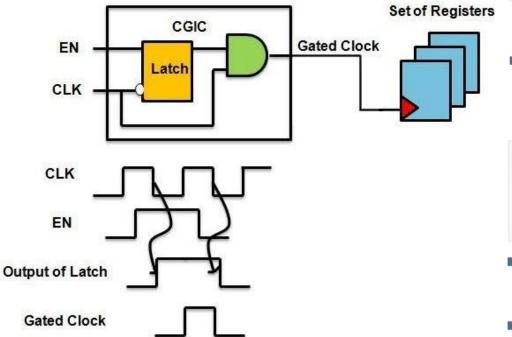

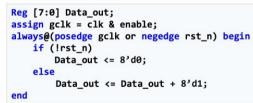

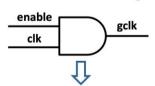

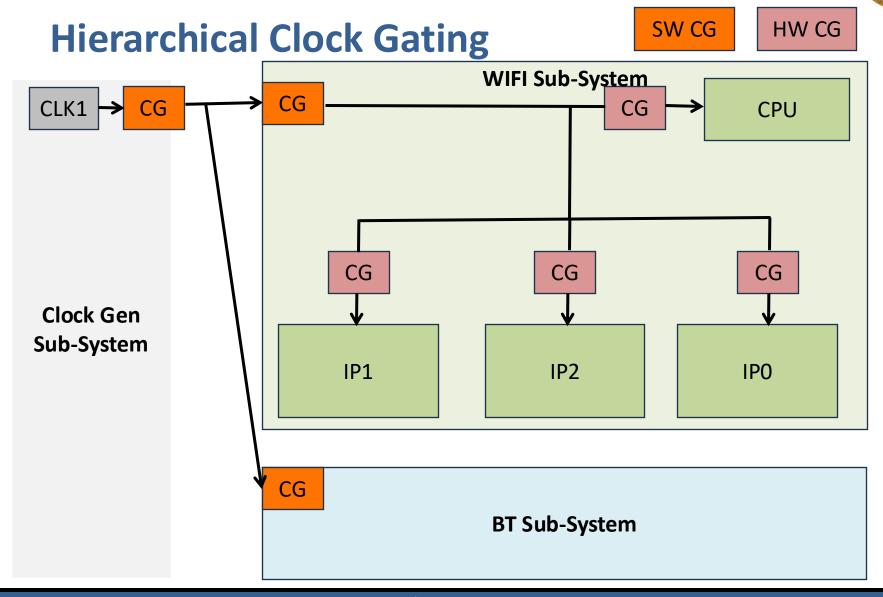

# **Clock Gating**

- Turn off the clock, when not use

- Scope: From module-level(TOOL) to sub-system level(Manual)

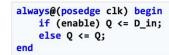

#### **Clock Gating (Auto CG)**

If Statement

Conditional Assignment

```

always@(posedge clk) begin

Q <= (enable)? D_in:Q;

end</pre>

```

Clock gating script style 1

```

insert_clock_gating

compile

```

Clock gating script style 2

```

compile -gate_clock

```

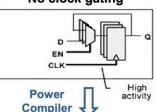

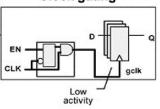

#### No clock gating

#### Clock gating

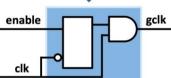

#### **Clock Gating (Manual)**

Clock gating script

replace\_clock\_gates compile

Report clock gating

report\_clock\_gating -gating\_elements

#### Recommended version\*

#### **Manual Clock Gating**

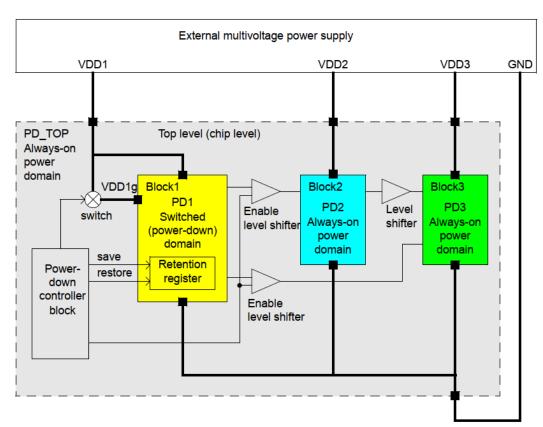

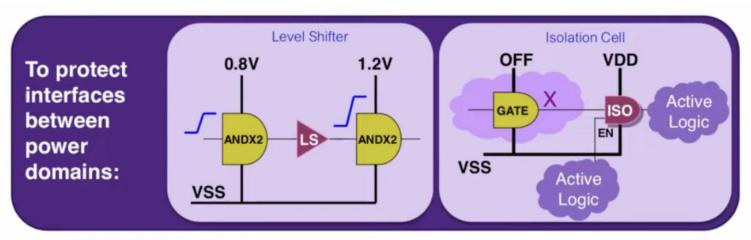

# Multi-VDD

Each sub-system requires the different voltage.

High Performerce(CPU, GPU...) -> High VDD

GND Normal Performance(Sec., Audio...) -> Low VDD

VDD

Isolation Control

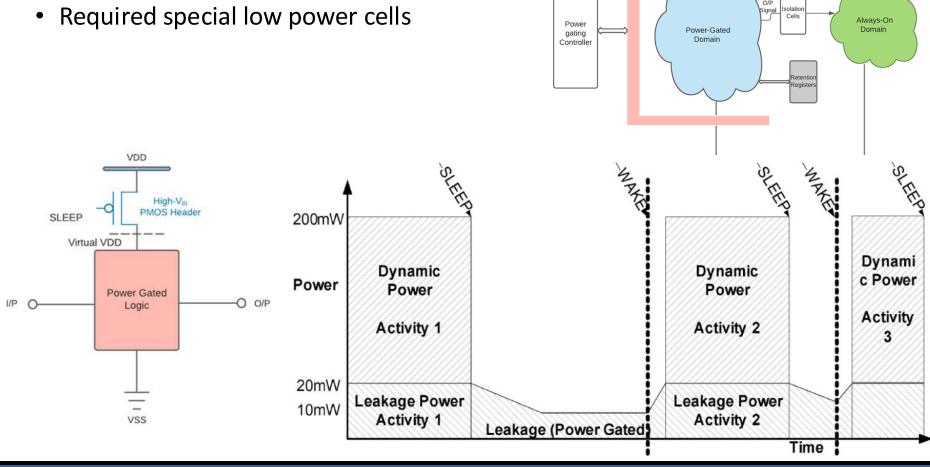

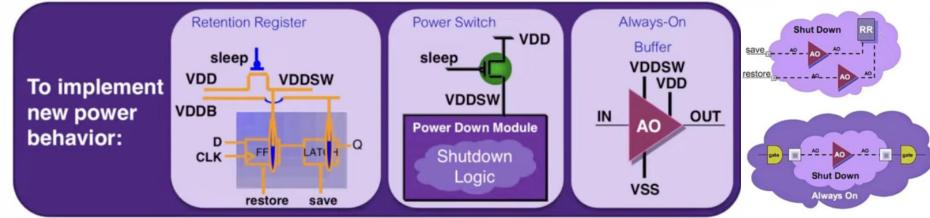

# **Power Gating**

Turn off the power, when not use

# **Special Low Power Cell**

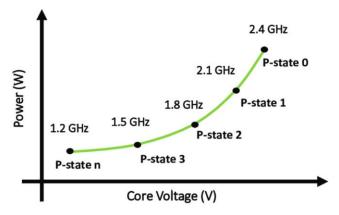

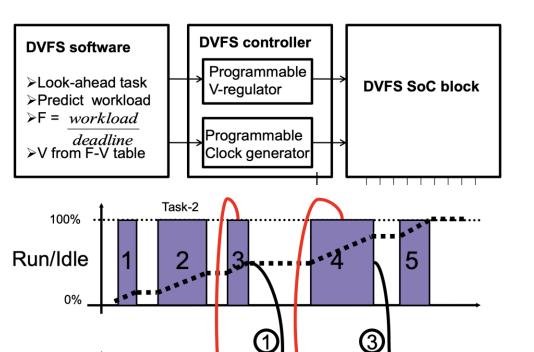

# **Dynamic Voltage and Frequency Scaling(DVFS)**

Adjust V and F to run just fast enough to meet the task

#### **AMD Turion MT-34**

| Frequency | Voltage | Power   |

|-----------|---------|---------|

| 0.8 GHz   | 0.90 V  | 6.25 W  |

| 1.0 GHz   | 1.00 V  | 9.65 W  |

| 1.2 GHz   | 1.05 V  | 12.76 W |

| 1.4 GHz   | 1.10 V  | 16.34 W |

| 1.6 GHz   | 1.15 V  | 20.41 W |

| 1.8 GHz   | 1.20 V  | 25.00 W |

100%

**DVFS**

Energy Saved

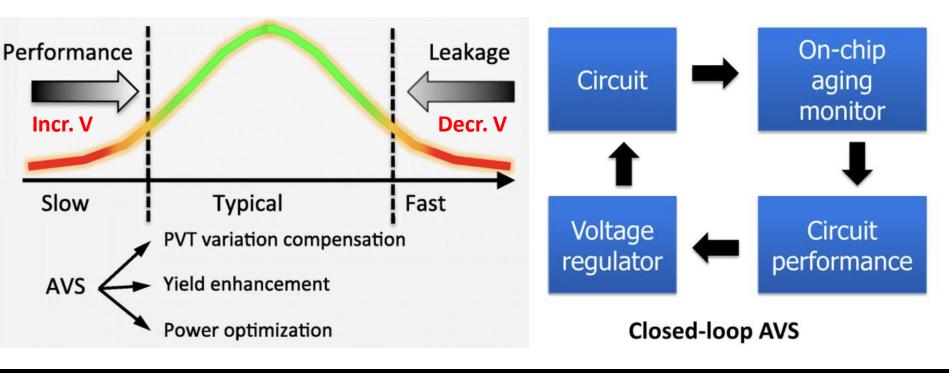

# Adaptive voltage frequency scaling (AVS)

- Adjusts the voltage to match the chip's minimum requirement.

- based on on-chip performance monitor

- Close-loop system for process and temperature compensation

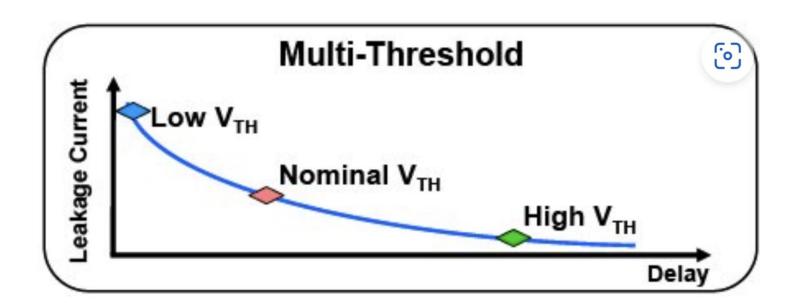

# Multi-Vt Cell

- Low Vt -> Critical Path -> Better Performance

- High Vt -> Non-Critical Path -> Save Power

- Cell selection will be automatically implemented by synthesis tool.

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

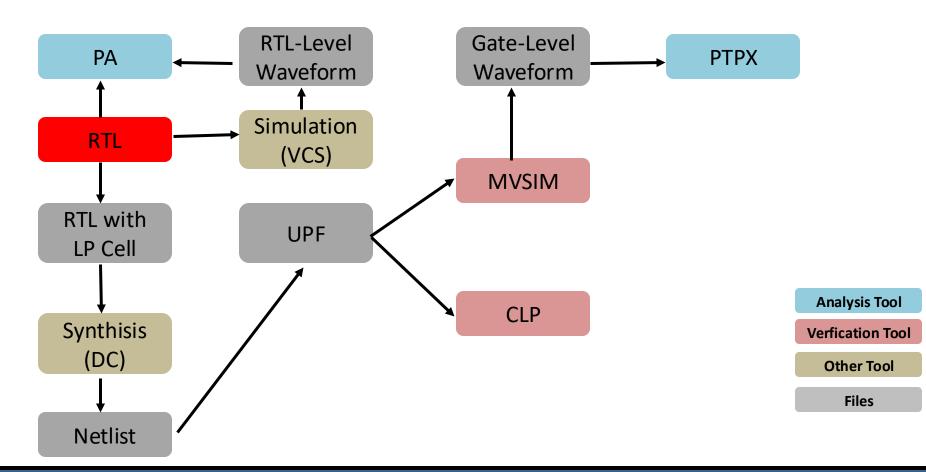

# **Low Power Design & Verification Flow**

- Motivation

- Power Consumption

- Low Power Design Techniques

- Low Power Design Tools & Flow

- SOC Low Power Design

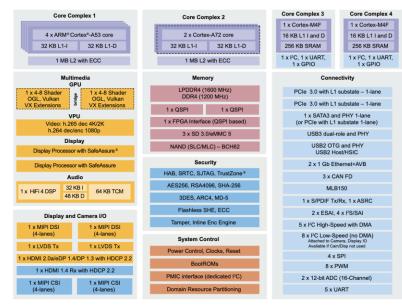

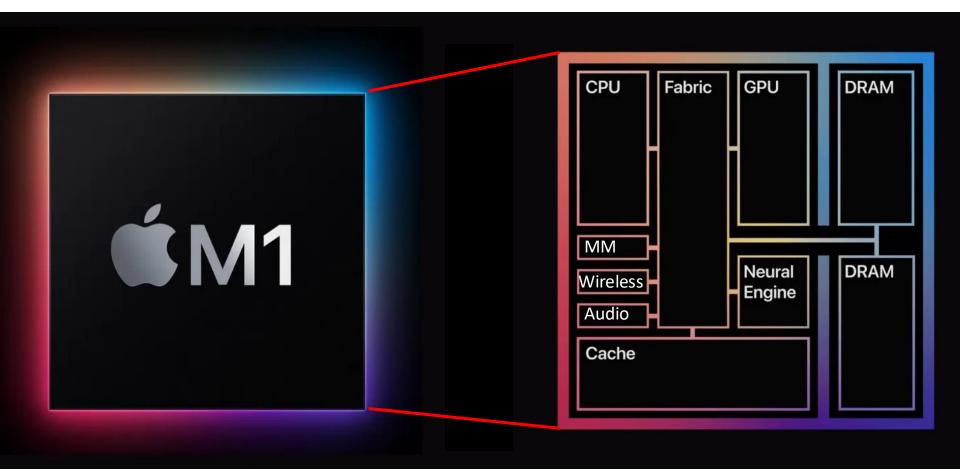

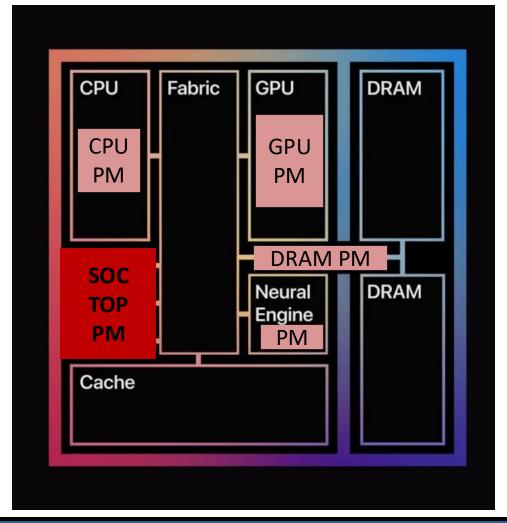

# Apple M1 SOC

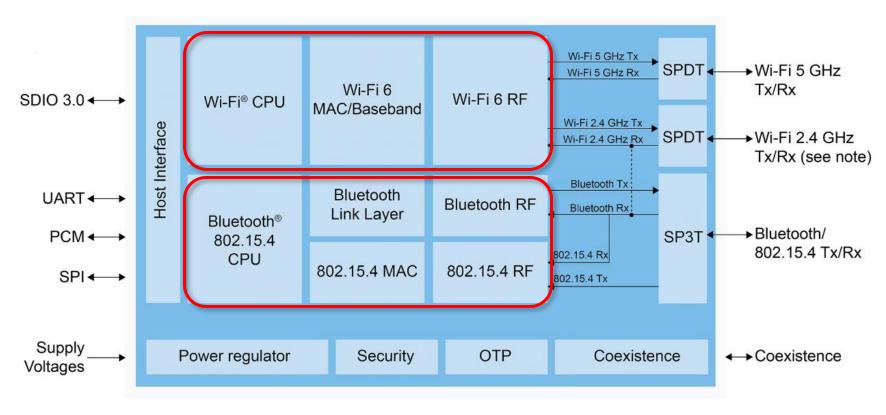

# Wireless Sub-System

Note: Optional simultaneous receive path between Wi-Fi, Bluetooth, and 802.15.4

# **Hierarchical Power Gating**

# **Hierical Low Power Control**

### References

- What is Low Power Design? Techniques, Methodology & Tools | Synopsys

- upf low power 1.1 (youtube.com)

- https://zhuanlan.zhihu.com/p/47483274

- The Ultimate Guide to Power Gating AnySilicon

- Low-Power IC Design: Techniques and Best Practices (ansys.com)

- Galaxy Low Power Solution (synopsys.com)

- Qnovo | I WANT MORE BATTERY CAPACITY IN MY SMARTPHONE

# **END**