### Introduction to SoC, Multimedia Systems, and ESL

### Outline

#### Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

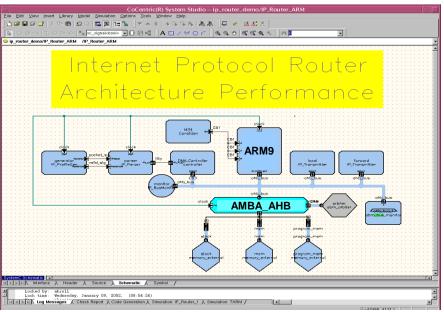

- Some existing system-level design tools

#### Conclusion

### Outline

#### Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

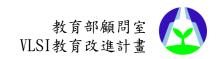

### **Silicon** Evolution

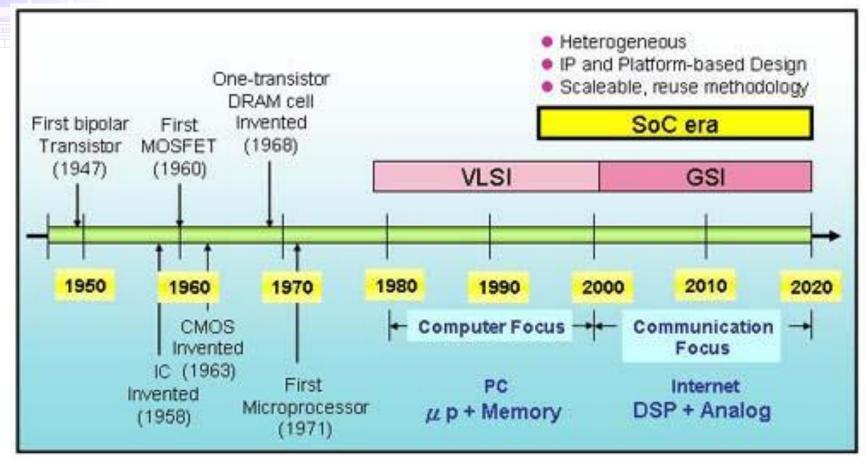

### Why System-on-a-Chip? Design Paradigm Shift

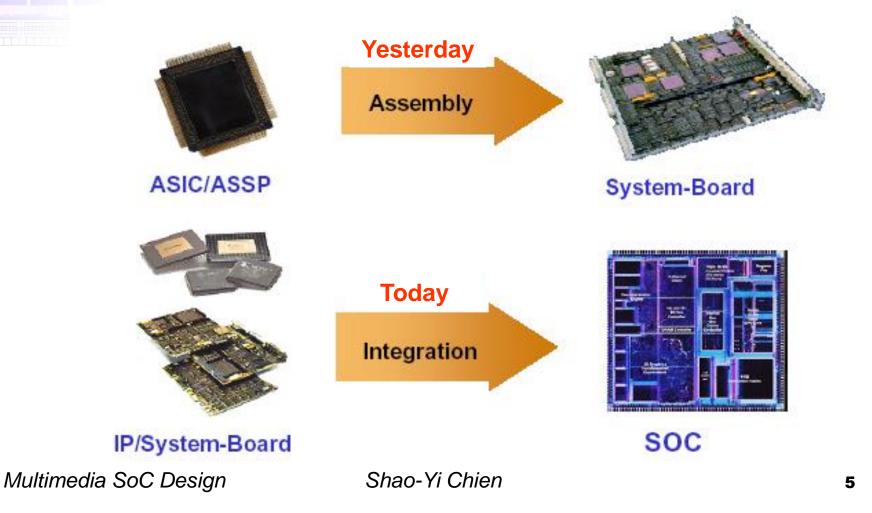

### Changes in the Nature of IC Design

6

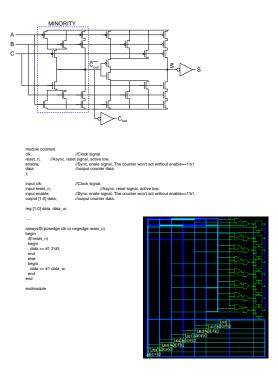

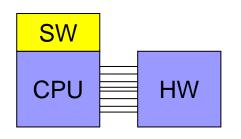

### From ASIC to SoC

#### Yesterday

HW onlyPerfect interconnection

HeterogeneousCPU + dedicated HW

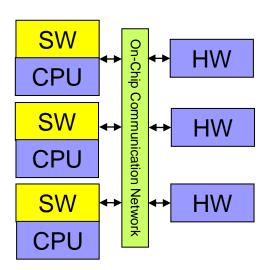

Today

Multiple SW stacksNon perfect interconnect

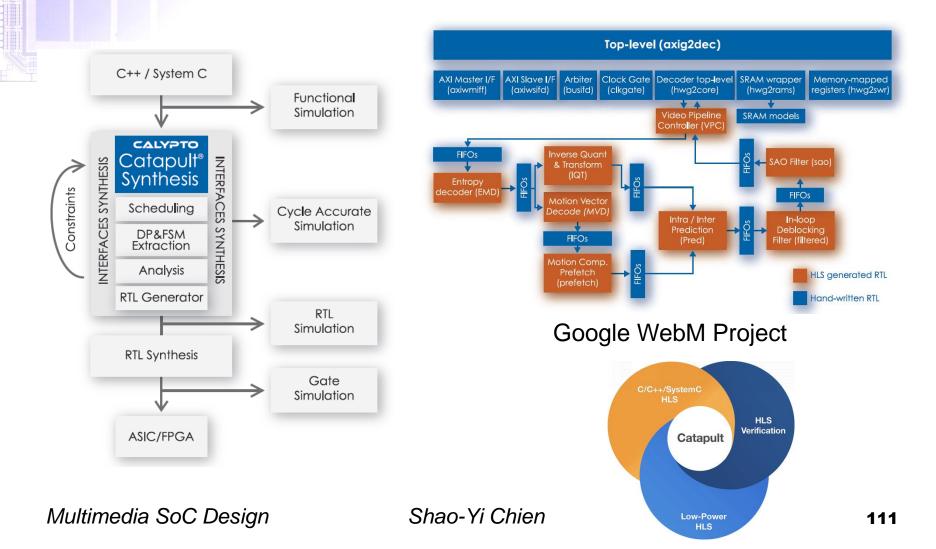

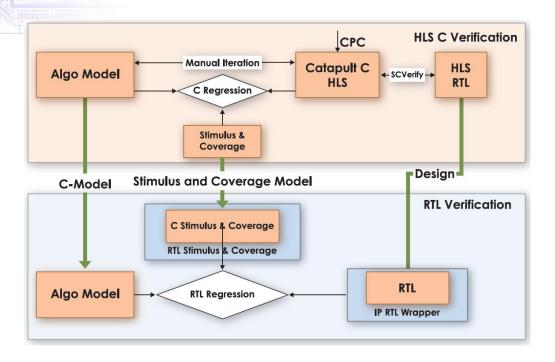

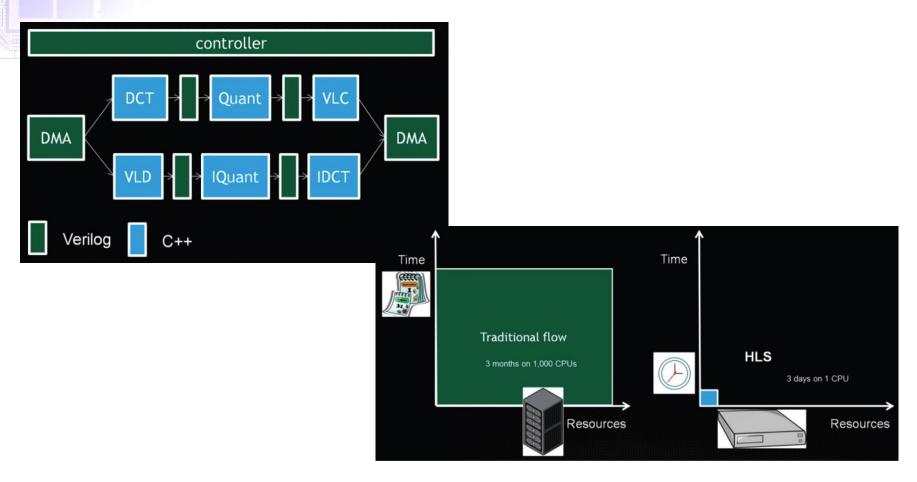

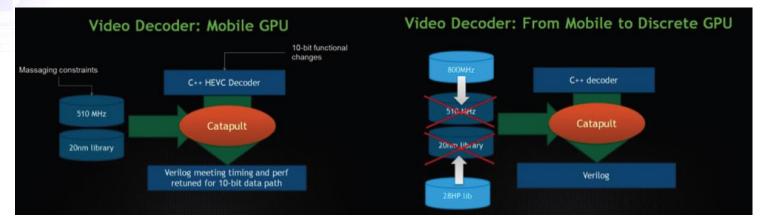

#### Multimedia SoC Design

### Outline

#### Introduction to SoC

## Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

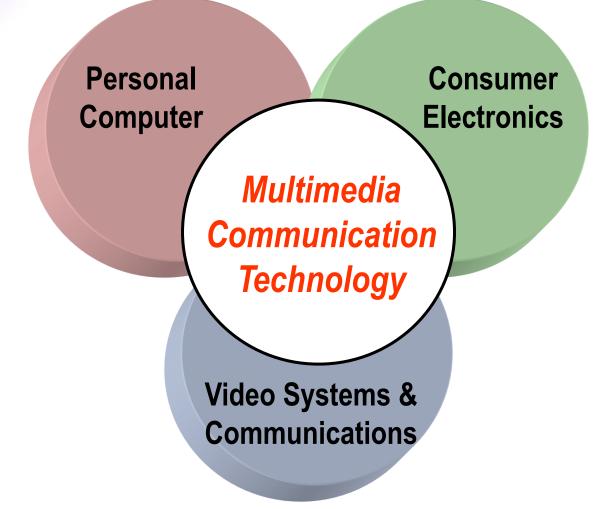

### **Digital Convergence**

Multimedia SoC Design

### Multimedia Technology for Human Life

- From office to home and the outdoors

- From large devices to portable devices

- From specific people to everybody

Any Time Any Where At Will

Multimed

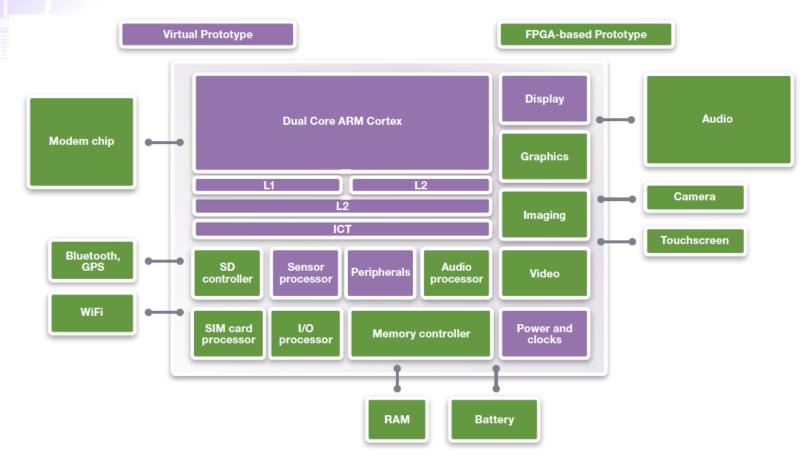

# Relationship between SoC and Multimedia Systems

Multimedia systems integrate many subsystems

□ User interface

- □ Image/video/audio capturing

- □ Image/video/audio displaying

- Image/video/audio processing and coding

- Communication and storage

- High volume of the consumer electronics

- Both the factors make multimedia system a highly possible application for SoC

- TV/STB, mobile phones, wearable devices, AR/VR, automotive electronics, multimedia players, multimedia portable players, game consoles, …

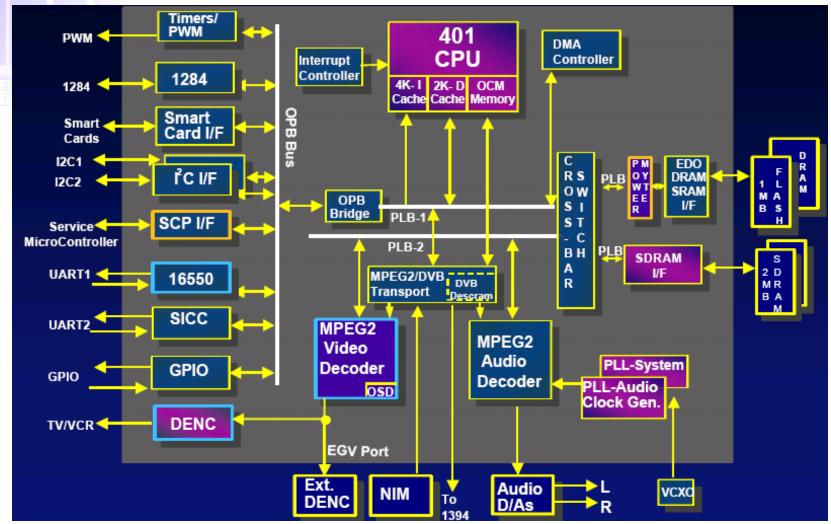

### SoC Example: Set Top Box Controller

Multimedia SoC Design

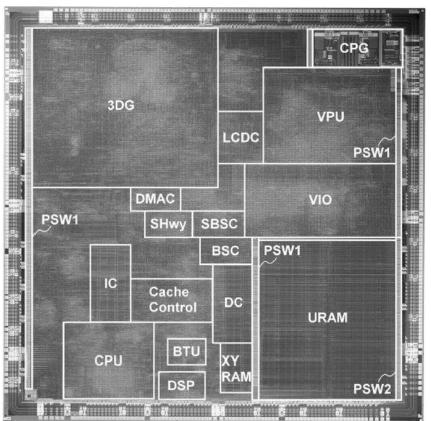

### SoC Example: Multimedia Mobile Phones (1)

Renesas application processor for 3G cellular phones

T. Kamei et al., "A resume-standby application processor for 3G cellular phones," *ISSCC Dig. Tech. Papers*, pp. 336—337, Feb., 2004.

Multimedia SoC Design

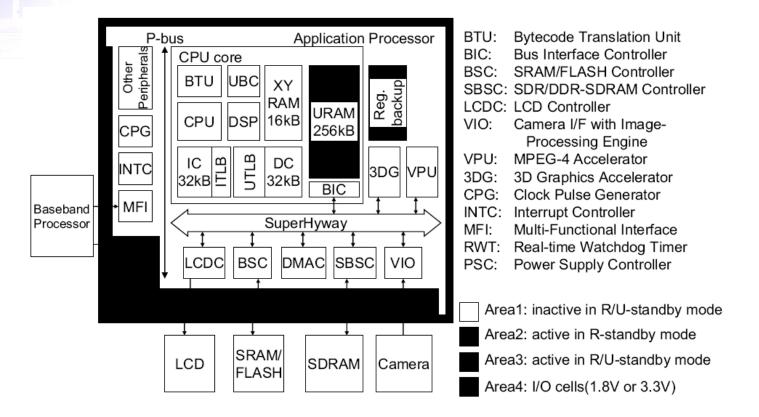

### SoC Example: Multimedia Mobile Phones (2)

T. Kamei et al., "A resume-standby application processor for 3G cellular phones," *ISSCC Dig. Tech. Papers*, pp. 336—337, Feb., 2004.

Multimedia SoC Design

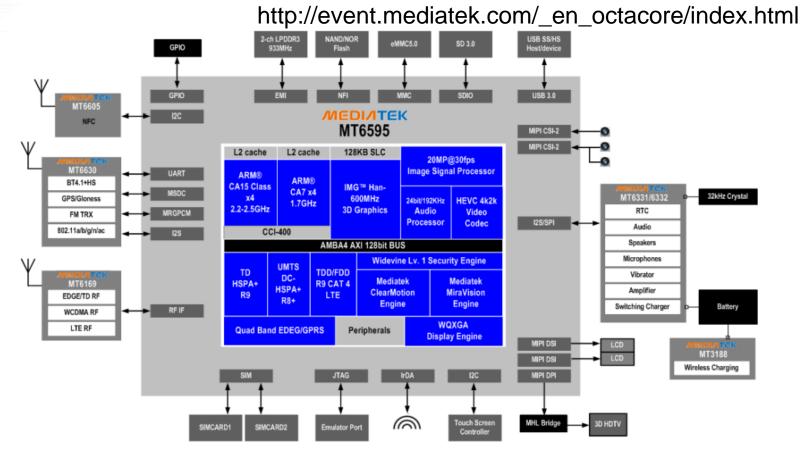

#### **MT6595 Platform Block Diagram**

Multimedia SoC Design

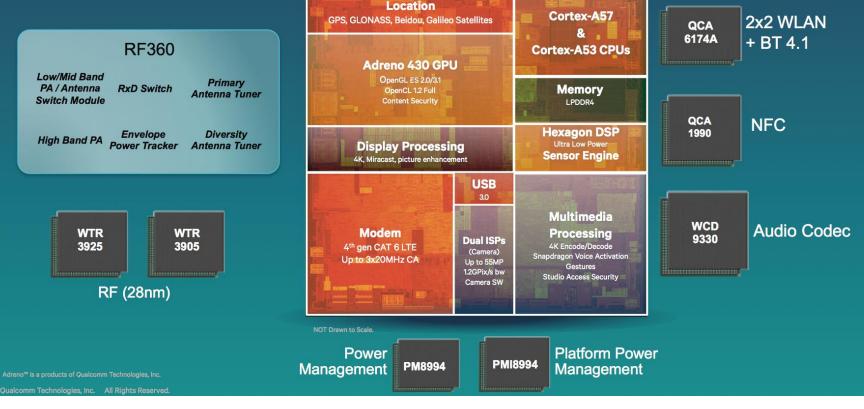

#### The Complete Snapdragon 810 Platform

Multimedia SoC Design

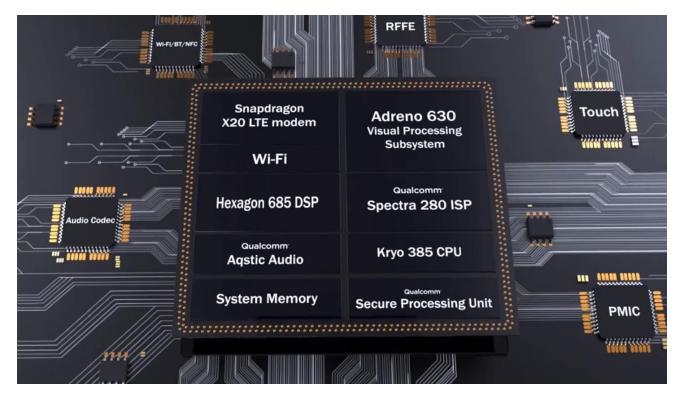

#### Snapdragon 845

Multimedia SoC Design

The World's First Smartphone SoC Chipset with a Dedicated Neural-network Processing Unit

Multimedia SoC Design

### Outline

Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

Multimedia SoC Design

### SoC Dilemmas

While SoC complexity is increasing, the time to market of consumer products is decreasing.

IC designer lacks expertise of system developers.

How to integration of internal virtual components (VC) and external VC?

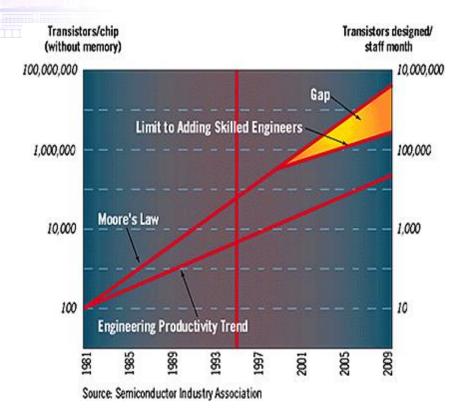

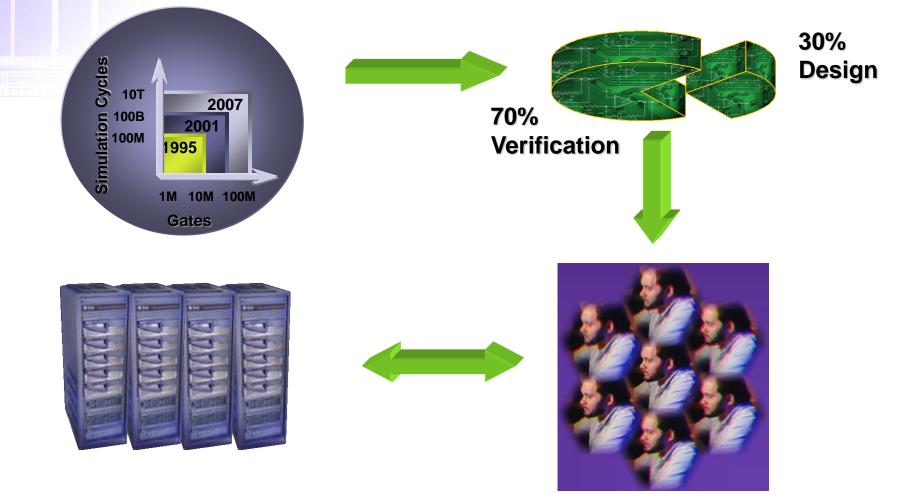

### Engineering Productivity Gap

- Engineering productivity has not been keeping up with silicon gate capacity for several years.

- Companies have been using larger design teams, making engineers work longer hours, etc., but clearly the limit is being reached.

### Challenges

#### Interoperability and Integration

- IPs (Intellectual properties) present a multitude of interoperability and integration challenges. System-Level Integration

- □ IPs may come in several forms: Hard, Soft, Firm

- Common interface between blocks?

### Challenges (cont.)

#### EDA Tool Interoperability

- □ These data formats may or may not be compatible.

- Standardizing these diverse data formats.

#### Testing an SoC

- □ An SoC's complexity requires extensive.

- □ It's necessary to test each VC separately.

- Process-Level Portability

- Soft IP & Firm IP

- Hard IP

### Outline

#### Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

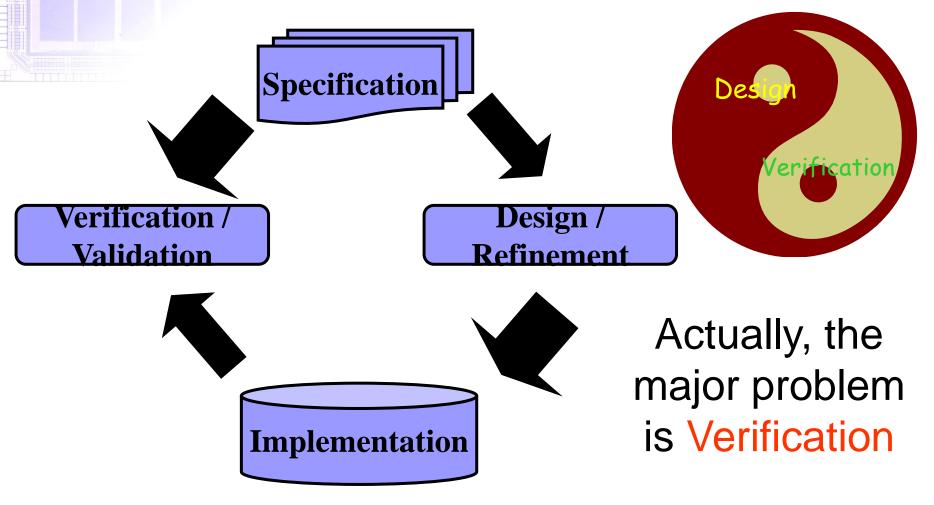

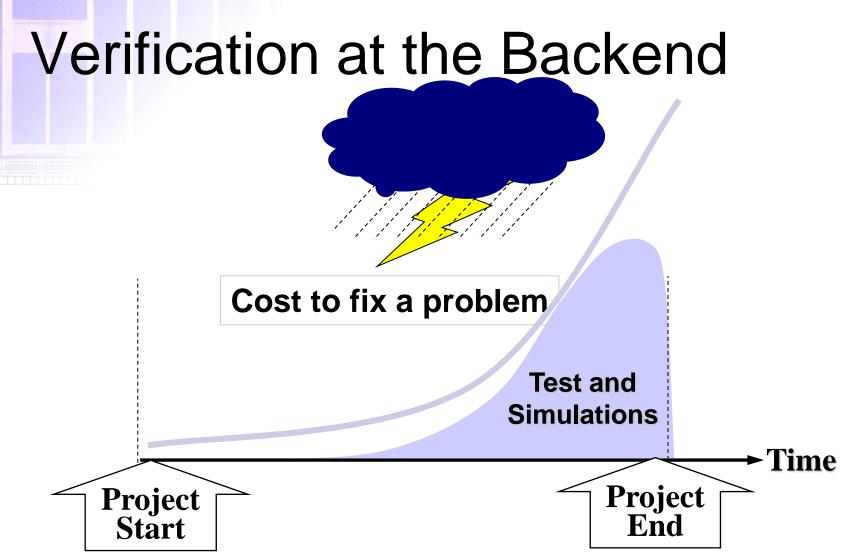

### **Design and Verification Step**

Multimedia SoC Design

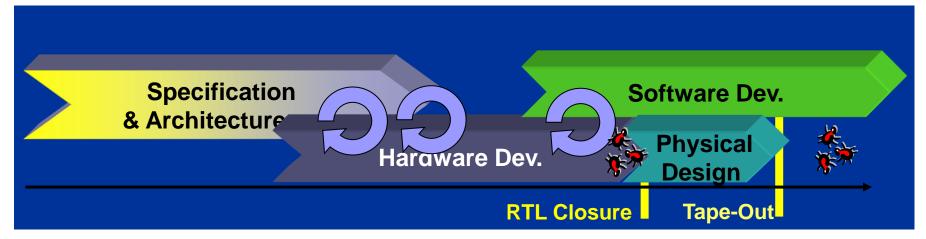

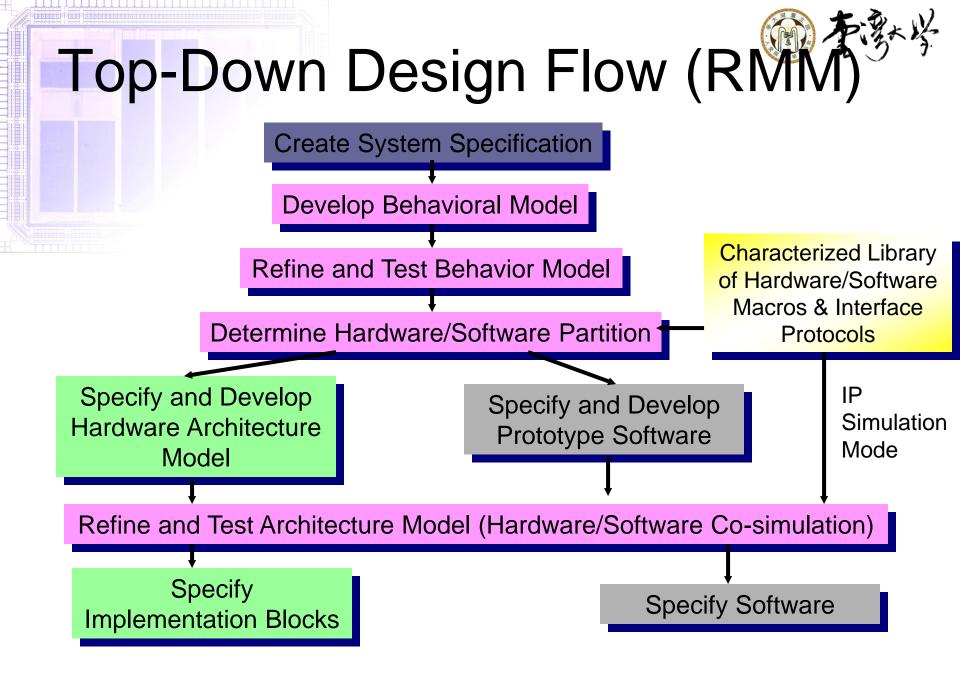

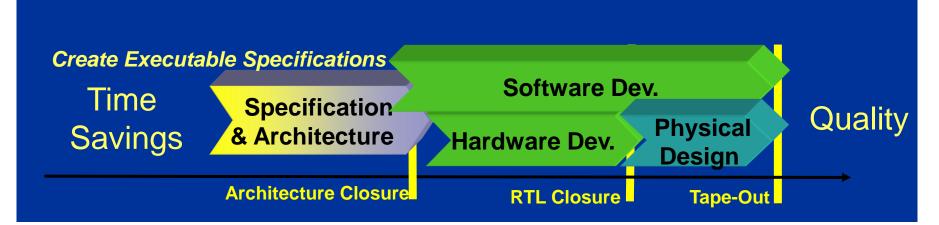

### Typical SOC design flow

Overlap in specification/architecture phase and RTL-design phase; multiple design changes

Architecture design done informally

SW development starting late in the project

Multimedia SoC Design

### **SoC** Verification Gaps

# Different languages are spoken At different levels of abstraction By HW / SW / systems people Problems, bottlenecks, and misunderstandings are detected too late.

Multimedia SoC Design

### **SoC** Verification Challenges

Multimedia SoC Design

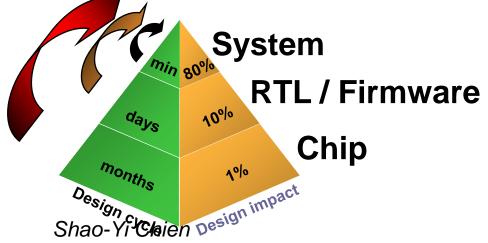

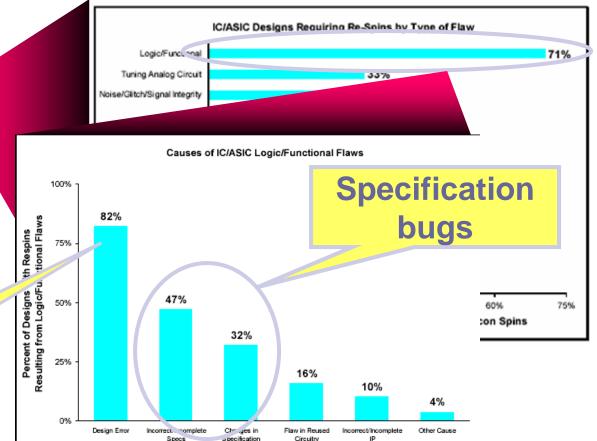

### System Level Design Matters

65% in 2003

61% of IC designs require one or more re-spins

Source: 2002 Collett International

**RTL bugs**

#### **Specification and RTL bugs cause re-spins!**

Multimedia SoC Design

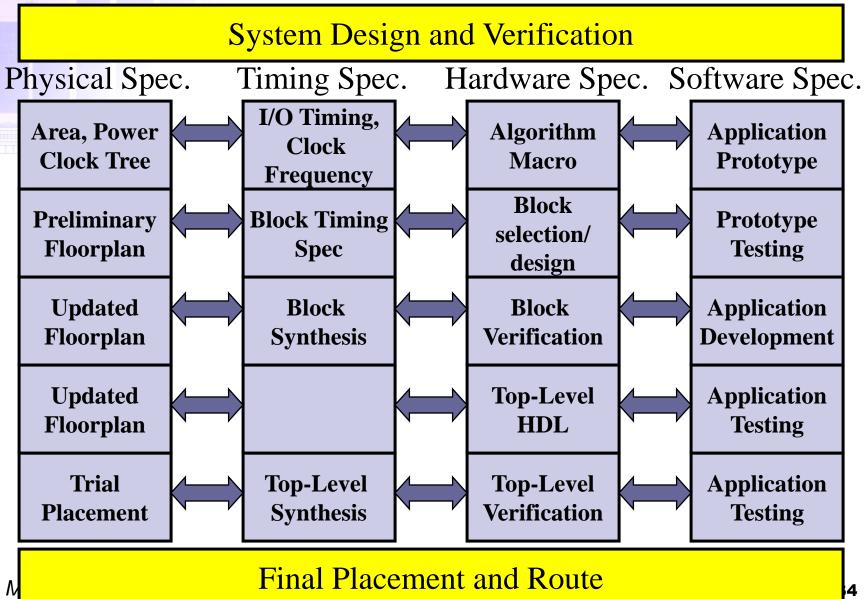

### SoC Design Methodologies

| System-Level IC<br>Architecture                                                                                             | <u>IP Sourcing</u>                                                               | IP Integration                                                                                                                                                     | <u>Chip</u><br>Implementation                                                                                                                                                                                       | Chip Fabrication               |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| <ul> <li>System Architecture</li> <li>Chip Architecture</li> <li>Technology Selection</li> <li>Algorithm Develop</li> </ul> | •In-house IP<br>+<br>•3rd party IP<br>•Selection<br>•Qualification<br>•Licensing | <ul> <li>Digital logic <ul> <li>+</li> </ul> </li> <li>•Mixed-signal</li> <li>•Embedded <ul> <li>Memory</li> <li>•Embedded</li> <li>Micro's</li> </ul> </li> </ul> | <ul> <li>•FPGA</li> <li>•Gate array</li> <li>•Standard cells</li> <li>•Megacell library</li> <li>•Datapath compiler</li> <li>•Memory compiler</li> <li>+</li> <li>•Hand-crafted</li> <li>•In-house tools</li> </ul> | •3rd party foundry<br>services |

Note:Shaded area is the conventional ASIC development process (Dr. H. D. Lin in 8th VLSI/CAD workshop)

Multimedia SoC Design

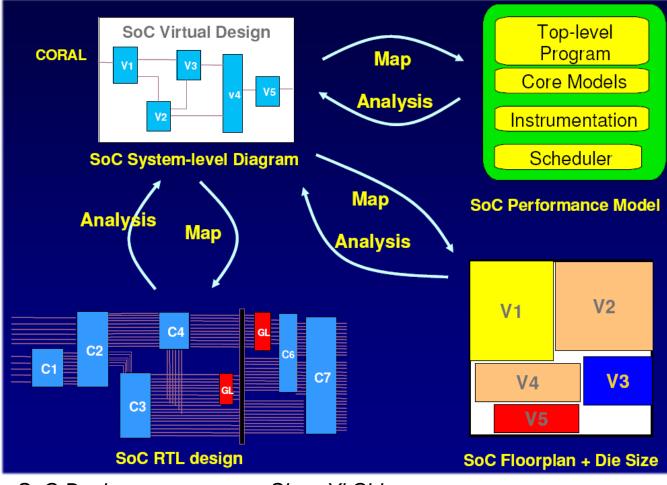

## Spiral SOC Design Flow (RMM)

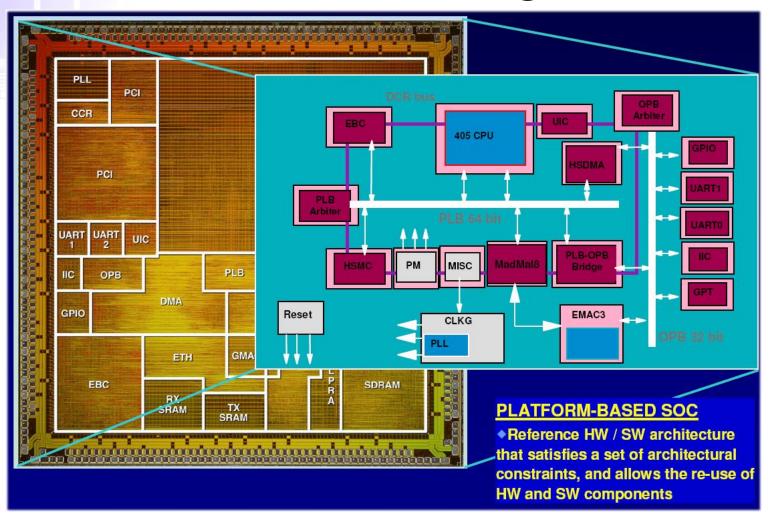

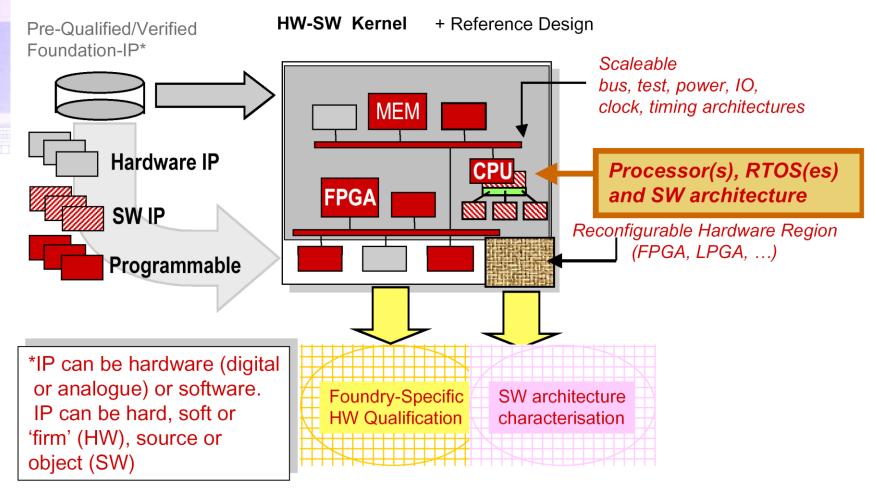

### **Platform Based Design**

Multimedia SoC Design

### **Platform Based Design**

#### Platform

An integrated and managed set of common features, upon which a set of products or product family can be built. A platform is a virtual component (VC).

#### Platform-based design

An integration oriented design approach emphasizing systematic reuse, for developing complex products based upon platforms and compatible hardware and software VCs, intended to reduce development risks, costs, and time to market.

### **Platform Based Design**

#### More precise definition of platform-based design

An organized method to reduce the time required and risk involved in designing and verifying a complex SoC, by heavy reuse of combinations of hardware and software IP. Rather than looking at IP reuse in a block by block manner, platform-based design aggregates groups of components into a reusable platform architecture.

#### System platform

A coordinated family of hardware-software architectures, satisfying a set of architectural constraints that are imposed to allow the reuse of hardware and software components

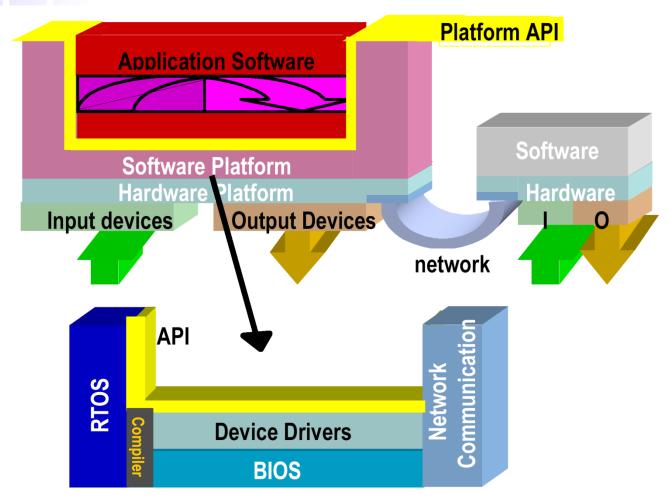

# A Hardware-centric View of a Platform

Source: Grant Martin and Henry Chang, ISQED 2002 Tutorial

### A Software-centric View of a Platform

Source: Grant Martin and Henry Chang, ISQED 2002 Tutorial

Multimedia SoC Design

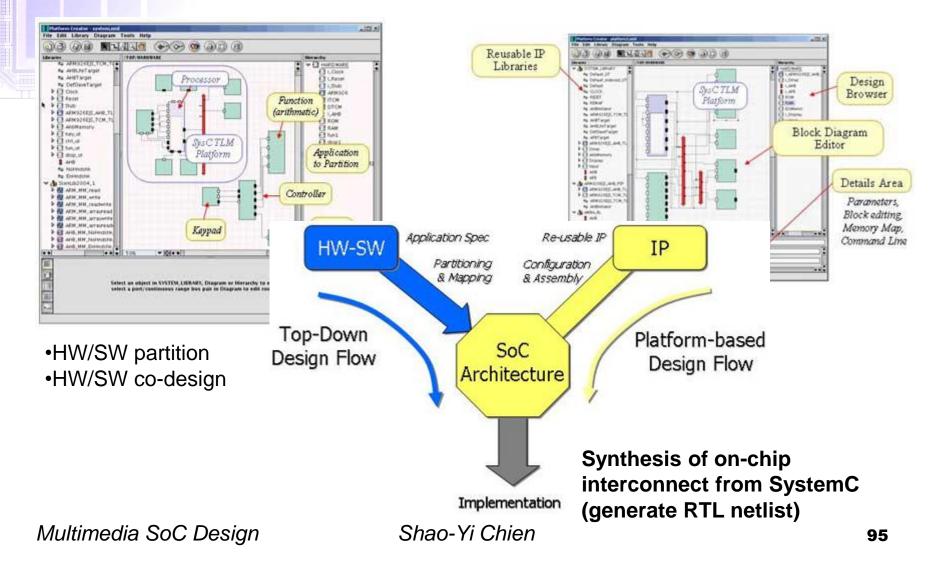

### Other Design Techniques/Problems

- Hardware/software partition

- Hardware/software co-design

- Hardware/software co-verification

### The EDA tool?

# Outline

#### Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

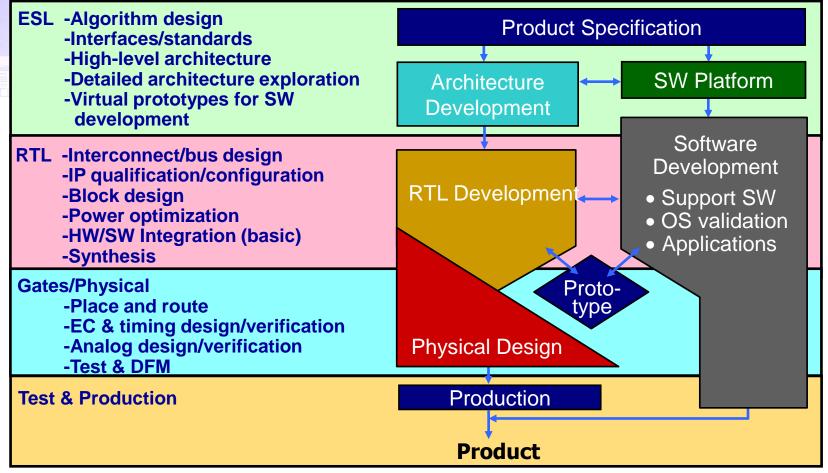

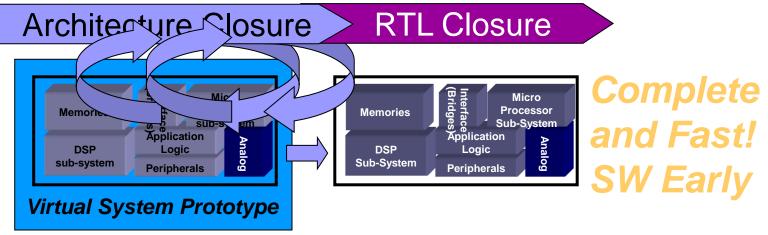

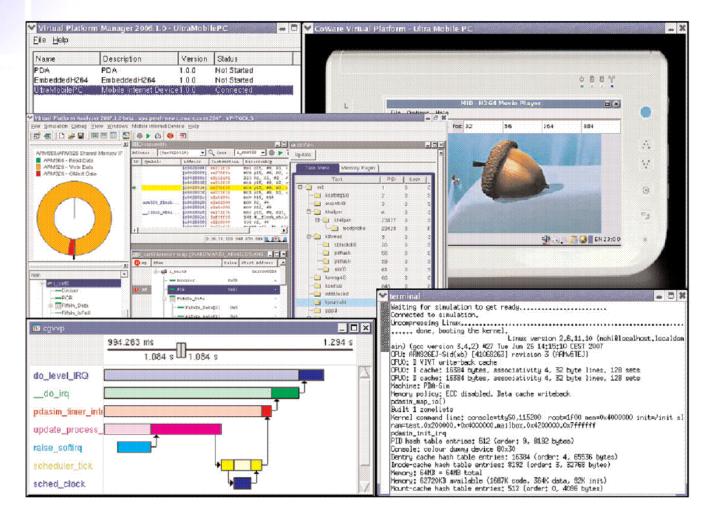

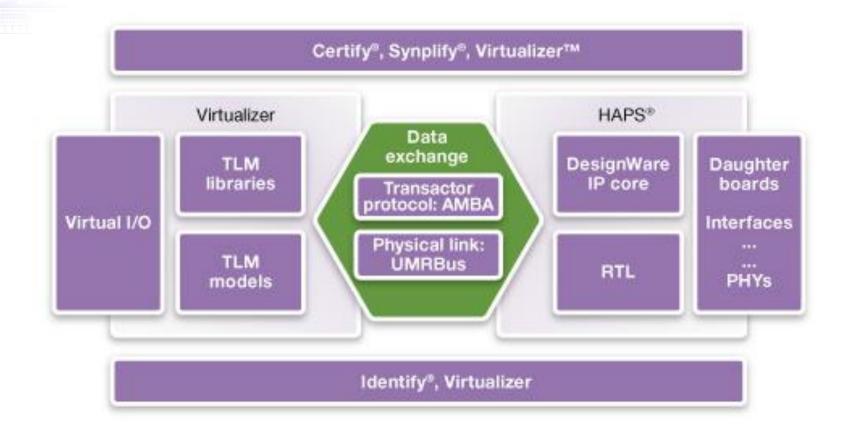

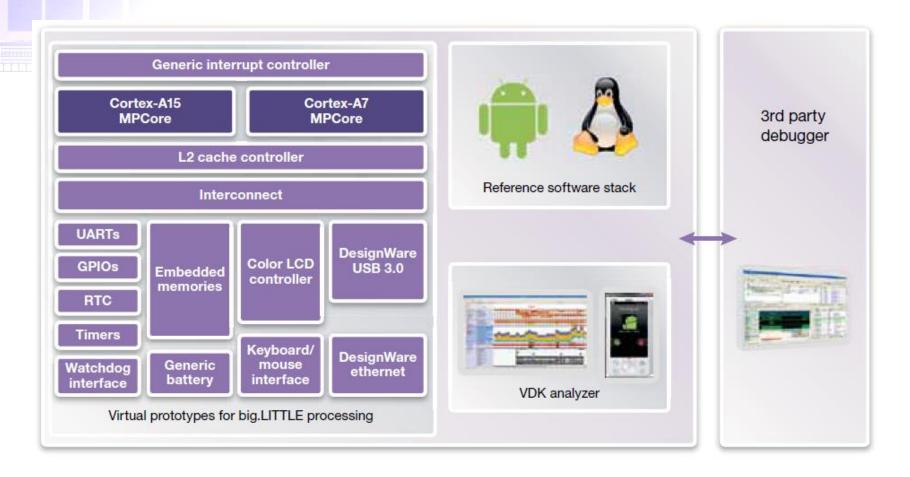

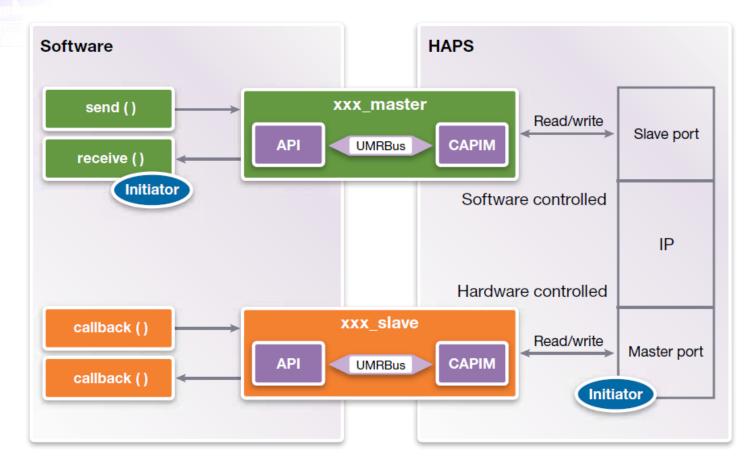

# Emerging SoC Design Flow (1/2)

The design methodologies developed for earlier SoC technology are inadequate to the task of designing a multiprocessor SoC

Electronic system-level (ESL) design methodology has been devised to solve these problems

#### Virtual Prototype

- A high-speed (20MHz or more) functional model of the target chip

- Can quickly assemble, simulate, and analyze alternative architectures

- Allows software development to start many months before a hardware prototype is available

Multimedia SoC Design

# Emerging SoC Design Flow (2/2)

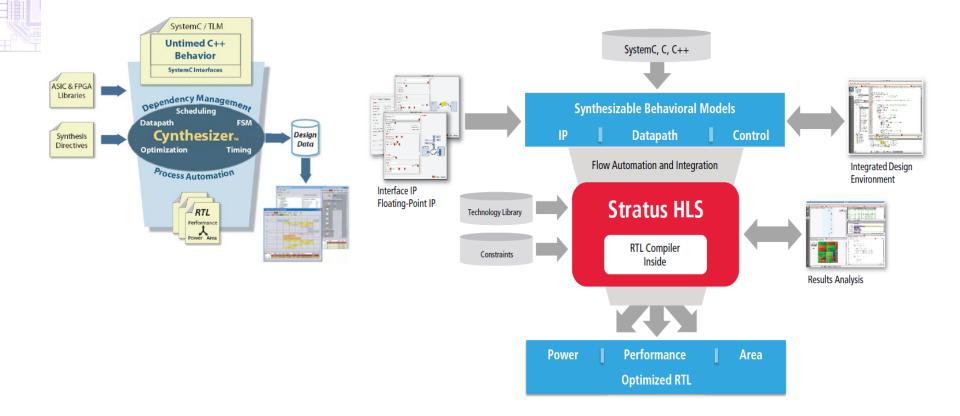

**ESL : Electronic System Level Design**

### Electronic System-Level (ESL) Design

A set of methodologies that enables SoC engineers to efficiently develop, optimize and verify complex system architectures and embedded software

The foundation for the continuously verifying downstream register-transfer level (RTL) implementation and subsequent software development

## **ESL:** New SOC Design Flow

#### Architecture closure

- □ Achieve a reduction # of RTL iterations

- Can perform concurrent HW and SW design

- Shorten the time it takes to get to golden RTL

### **Architectural Closure**

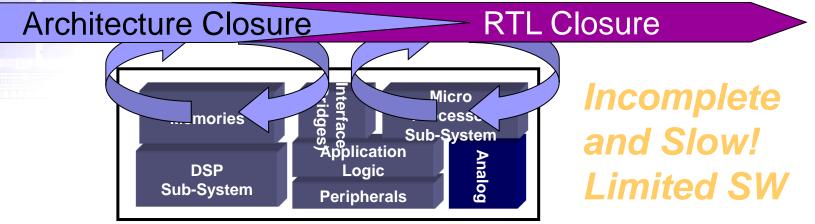

Model the entire system (HW & SW) to verify that it meets the performance goals optimally

□ Validate the architecture

- Eliminate bottlenecks in Bus transactions

- Refine data buffer structure/management

- Close on HW/SW partitioning

- □ Perform software-based testing

- Verify system setup, peripheral drivers and key application SW features

- Optimize timing-critical tasks of the embedded software

### RTL Closure Goal: Implement and verify the architecture in RTL

#### Individual block (IP) level

- Implement/synthesize RTL blocks or

- Import (& re-validate) design IP

- "Prove" block-level functionality and performance

- Check conformance to specifications/standards

#### □Full chip level

- Resolve micro-architecture corner cases (clock domains, FIFOs, handshakes, split Bus transactions)

- Integrate imported IP, show chip-level integrity

- Perform software execution (reset.....)

## **SOC** Design Flows

Typical Flow: Step 1 and 2 performed on RTL model

#### New Flow: Step 1 on transaction level, step 2 on RTL model

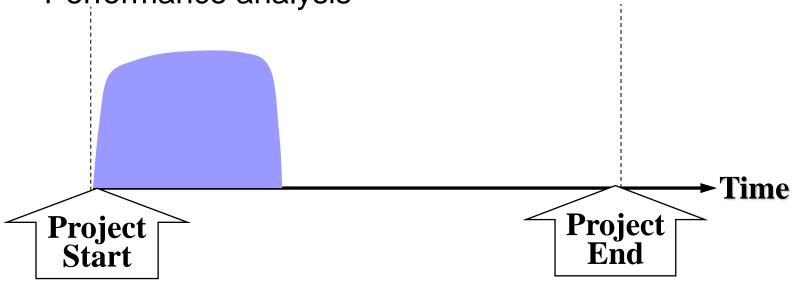

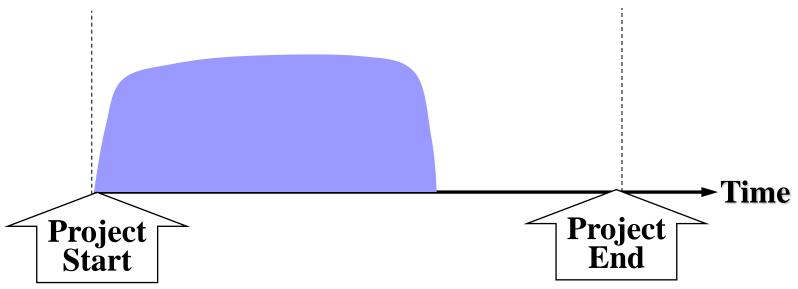

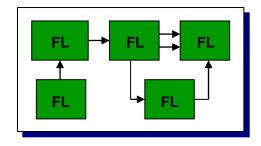

# **Continuous** Verification (I)

- High Level Analysis

- Functional verification

- Architecture exploration

- Performance analysis

- Executable specification

- High-level testbench

- SW development platform

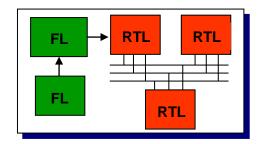

# Continuous Verification (II)

- "Mixed" Level Analysis

- Functional verification

- Architecture validation

- Performance validation

- Re-used IP

- Detailed design of components/subsystems

- More detailed testbench

# **Continuous** Verification (III)

Implementation verification

- Detailed design of system

- Fully detailed testbench

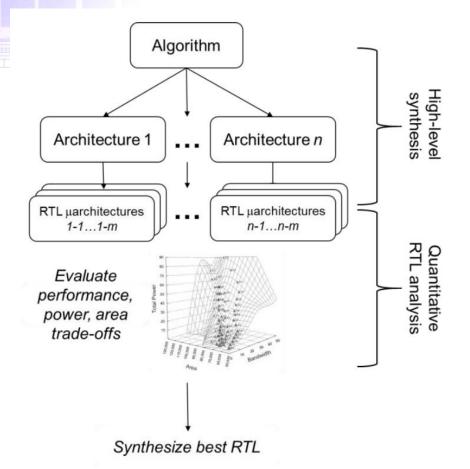

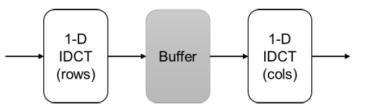

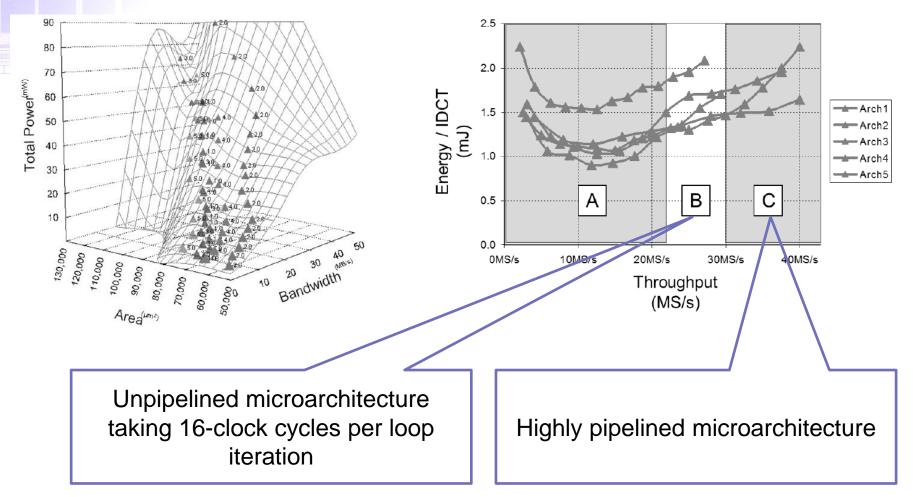

### **Design Space Exploration**

# Outline

#### Introduction to SoC

- Relationship between SoC and multimedia systems

- Challenges for SoC Design

- SoC design methodologies

- New SoC design methodologies: ESL

- Modeling issues

- Some existing system-level design tools

#### Conclusion

Multimedia SoC Design

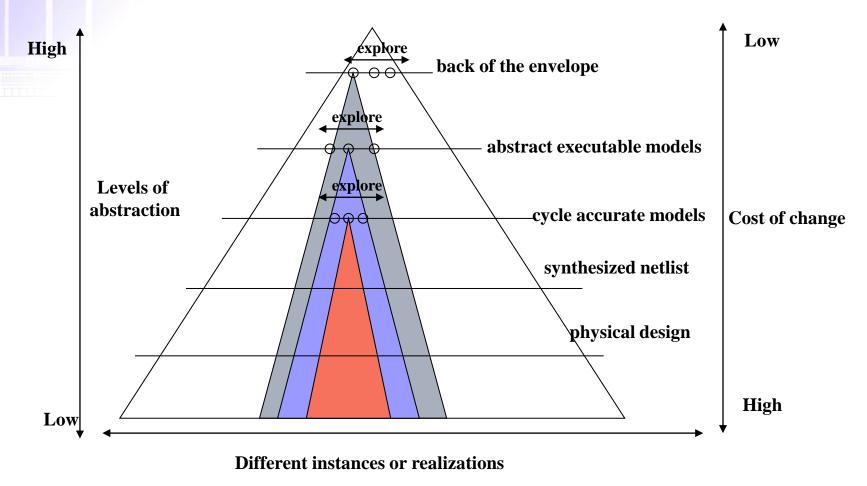

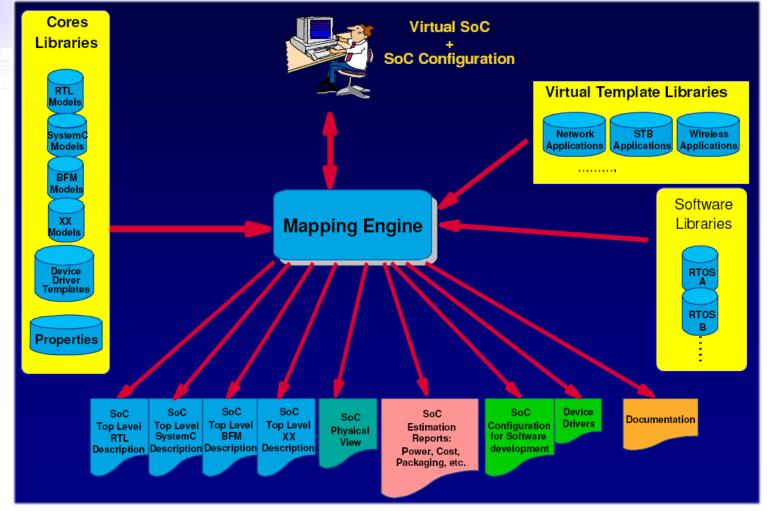

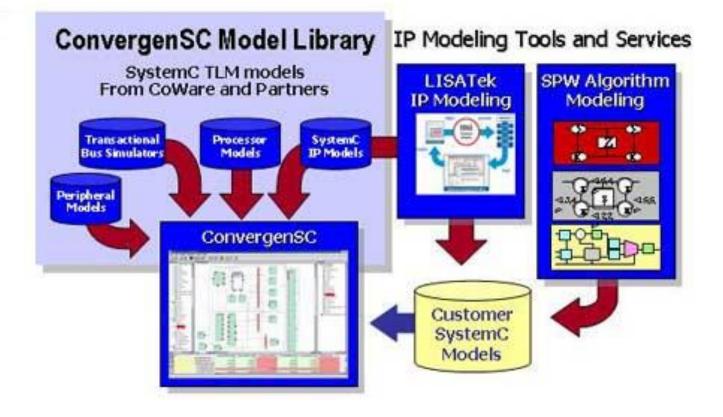

## Modeling issues

System-level design tools will be integrated into the new SoC design flow

Also called as Electronics System Level (ESL) tools

- Have benefits in system verification and hardware-software co-design

- Good modeling is the key for successful system-level design

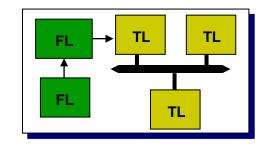

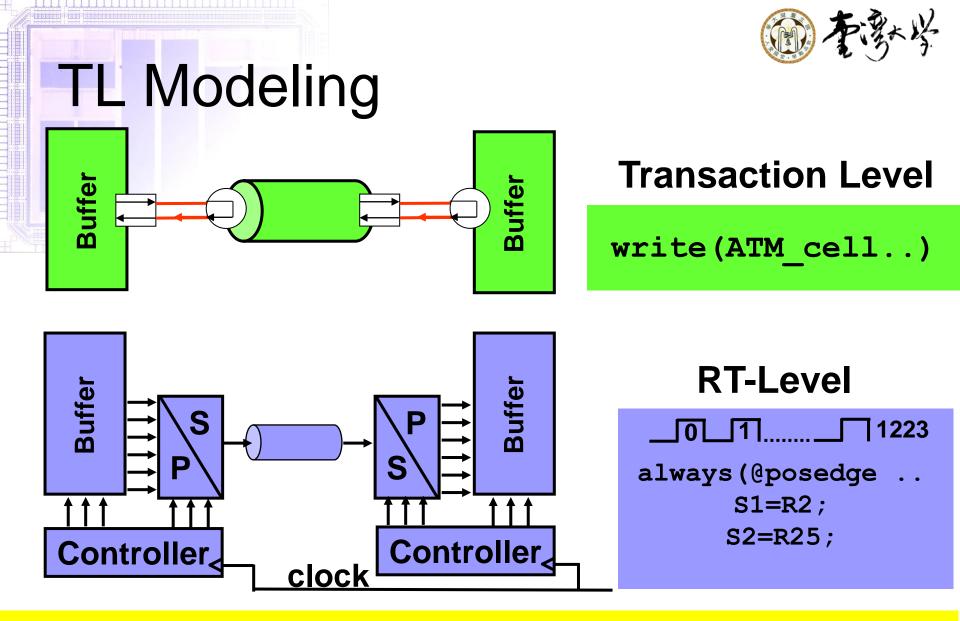

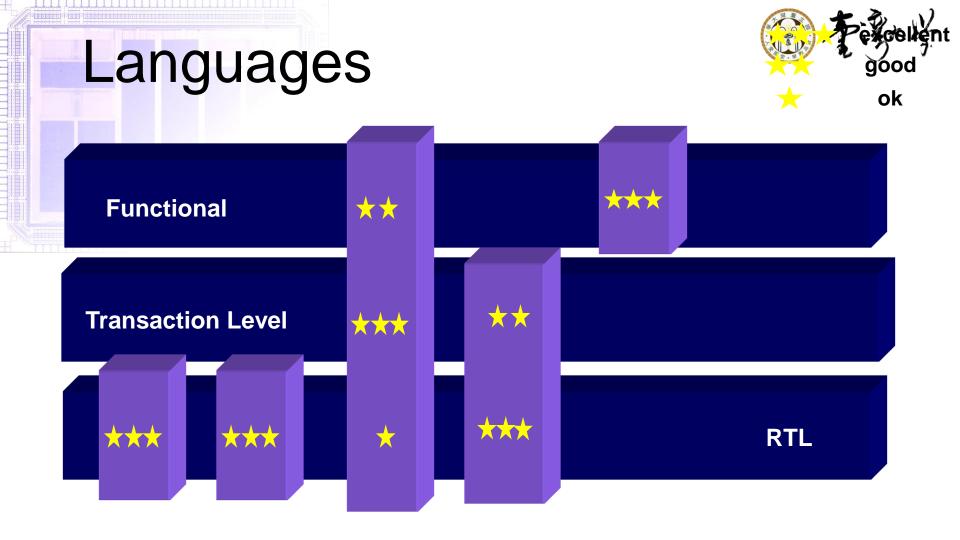

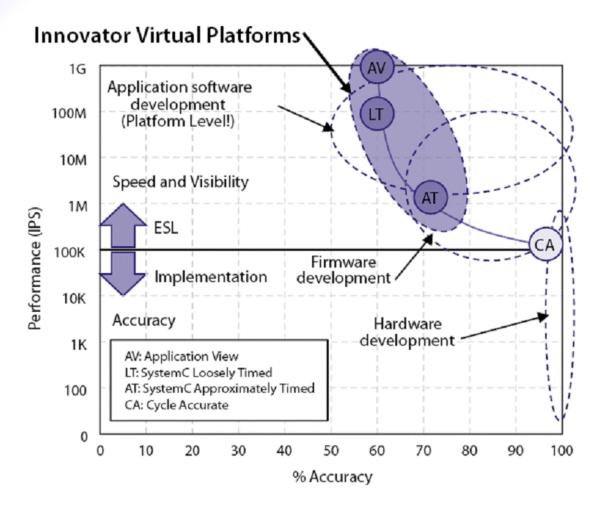

## Levels of Abstraction

- Functional Level

Algorithm optimization

Dropped calls/bit error rate

- Transaction Level

- Architecture closure

- Software verification

- Bus bandwidth / cache size

- RT-Level

- Detailed hardware design

- handshake / timing issues

Multimedia SoC Design

#### Simulation speed requirements :: 100-1000x

Multimedia SoC Design

### Functional Level Modeling High Performance

| Functionality  | Yes            |

|----------------|----------------|

| Cycle Accurate | No             |

| Timing         | No             |

| Pin Accuracy   | No             |

| Communication  | Point to Point |

| Channels       | FIFO           |

| Parameters     | Yes            |

## **Functional Modeling - Benefits**

#### High Performance

- potential for 1000x speed over RTL

- Model the "complete" system and environment

- provides a functional testbench that can be used during implementation

- System level analysis capabilities

- Libraries of standard protocols jumpstart modeling efforts

- e.g., CDMA/Bluetooth reference design kits

Multimedia SoC Design

### **Transaction Level (TL) Modeling**

| Functionality  | Yes             |

|----------------|-----------------|

| Cycle Accurate | Not necessary   |

| Timing         | No              |

| Pin Accuracy   | No              |

| Communication  | Shared          |

| Channel        | User defineable |

| Parameters     | Yes             |

One Transaction >>>>>>> 1000 signals toggling 1000 times

# **TL Modeling**

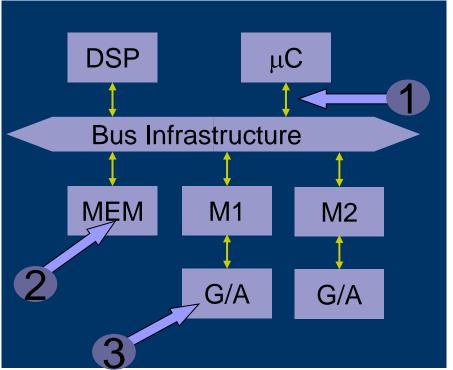

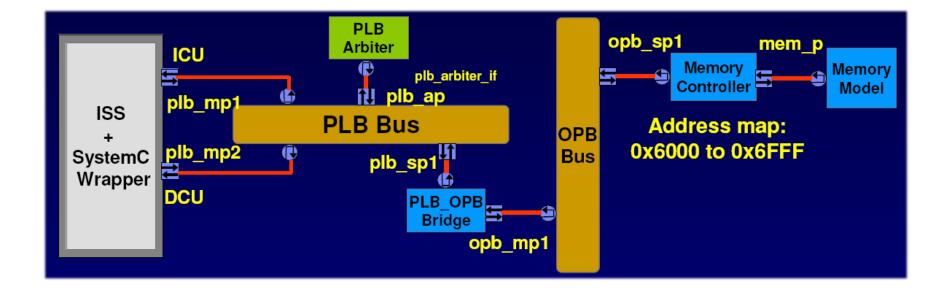

Transaction level modeling focuses on the communication between concurrent functional modules through the (on chip) bus infrastructure

- 1. All modules have <u>well defined</u> procedural interfaces to communicate with other modules

- 2. Modules model the function and (context sensitive) <u>latency</u> between request/response

- 3. <u>Sources</u> and <u>sinks</u> model real world data rates

- Processor, packet streams, etc.

Multimedia SoC Design

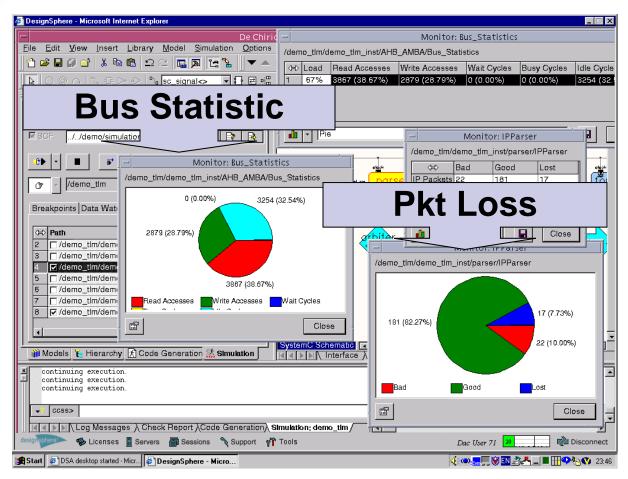

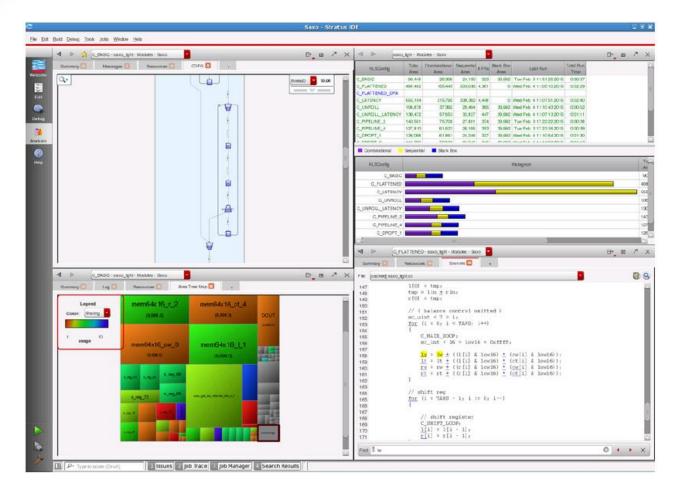

## **Fast Architecture Verification**

#### **Design Capture**

- multiple levels of abstraction

- graphical, textual

Debug of HW & SW

- source code debug

- memories, buses, interrupts

- **Performance Analysis**

- interactive traces and statistics

#### Closing on the Architecture at the Transaction Level reduces Risk by 80%

## TL Modeling Bus and Memory Analysis

| De Chirit       Monitor: mem         Die Edit View Inset Labrary Model Simulation Options       Monitor: mem         Options       Monitor: Market       Monitor: Market         Options       Monitor: Market       Monitor: Market         Options       Monitor: Transfer       Monitor: Transfer       Monitor: Transfer         Monitor: Transfer       Monitor: Transfer       Monitor: Transfer       Monitor: Market       Monitor: Market         Monitor: Transfer       Monitor: Market       Monitor: Market       Monitor: Market       Monitor: Market         Monitor: Transfer       Monitor: Market       Monitor: Transfer       Market       Monitor: Market       Market       Monitor: Market         Monitor: Transfer       Monitor: Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DesignSphere - Microsoft Internet Explorer                                                                                                                                                                                                                |                                                                                                      |              |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------|--|--|

| File       Edit View Insert Library Model Simulation Options         //demo_tim/demo_tim/inst/mem/mem          //demo_tim/demo_tim/inst/mem/mem         //demo_tim/demo_tim/inst/mem/mem         //demo_tim/demo_tim/inst/mem/mem         //demo_tim/demo_tim/inst/mem/mem         //demo_tim/demo_tim/inst/mem/mem         //demo_tim/demo_tim/inst/demo_single s         //demo_tim/inst/demo_single s         //demo_tim/inst/demo_tim/inst/demo_single s         //demo_tim/inst/demo_tim/inst/demo_single s         //demo_tim/inst/demo_tim/inst/demo_single s         //demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_tim/inst/demo_t                                                                                                                                                                                                                                                                                                                                                                          | De Chiri                                                                                                                                                                                                                                                  | Monitor: mem                                                                                         | · -          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                           | /demo_tlm/demo_tlm_inst/mem/mem                                                                      | 1            |  |  |

| Image: Second                                | 1 🖆 🖬 🕼 🖆 👗 🛍 🛍 🗅 📿 🛄 🗖 🖽 🦹 🔍 🔺                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| demo_tim       (ids/chome/dac/dac/71/dem X Seject.)         # SCF:       // demo/simulation/demo_single.s         # SCF:       // demo/simulation/demo/single.s         # SCF:       // demo/simulation/demo/singl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                           | المتعاد الأعاما الأعامة الأخاصة الأدامي الأدامي الأدامي الأدامي الأدامي الأدامي الأدامي المتعاد الات | -            |  |  |

| demo_tim       (idds/choms/dac/dac71/dem X       Select         # SCF       //./demo/simulation/demo_single s       >         # SCF       //./demo_tim       >       >       >       >       >         # Geno_tim       Imme       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       >       ><                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| Clear         Clear         Clear         Clear         Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           | 00001020 09 0A 0B 0C 0D 0E 0F 10 13 12 11 10 11 11 11                                                |              |  |  |

| M SGP       J. demo/simulation/demo_single.s       Image: Simulation/demo_single.s       Image: Simulation/d                                                                                                                                                                                                                                                                                                                                                                                                                                   | demo_tlm (/ids/chome/dac/dac71/dem 🔨 X Select                                                                                                                                                                                                             | 00001030 00 00 00 00 00 00 00 00 00 00 00 00                                                         | 1 1          |  |  |

| 00001050 00 00 00 00 00 00 00 00 00 00 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 🛛 🖉 SCE 🔢 / /demo/simulation/demo. single s 😑 🕞 🕞                                                                                                                                                                                                         |                                                                                                      | bout         |  |  |

| Image: Stress                                |                                                                                                                                                                                                                                                           |                                                                                                      | route.       |  |  |

| Image: Sevent                                |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| Breakpoints       Data Watch Level Watch Montors         Ital S:       /demo_tlm/demo_tlm_inst/AHB_AMBA/Transfer_Trace         Ital S:       /demo_tlm/demo_tlm_inst/controller idle         Ital S:       /demo_tlm/demo_tlm_inst/controller idle <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| Breakpoints Data Watch Level Watch Montors       00001040 00 00 00 00 00 00 00 00 00 00 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| Breakpoints [Data vrach] Evel vrach       Nonitors         Image: State vrach       Nonitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| G: Path       Image: Close       Image: Close         Image: Close       Image: Close       Image:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Breakpoints Data Watch Level Watch Monitors                                                                                                                                                                                                               |                                                                                                      | AHU ANGA AHU |  |  |

| Line Close C |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| Amountain and a second seco                                |                                                                                                                                                                                                                                                           | 🖬 🔹 Line 🔽 🖬 Close                                                                                   |              |  |  |

| /demo_tlm/demo_tlm_inst/AHB_AMBA/Transfer_Trace         102.5: /demo_tlm/demo_tlm_inst/sw read addr: 0x0000102c; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [ABM_0KAY]         103.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         104.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/amm_data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/amm_data value: no value         107.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/amm_data value: no value         108.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/amm_data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem_data value: 0x10111213 [ABM_0KAY]         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem_data value: no value         111.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem_data value: no value         111.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| 102.5: /demo_tlm/demo_tlm_inst/sw read addr: 0x0000102c; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [ABM_0KAY]         103.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [ABM_0KAY]         104.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [ABM_0KAY]         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         106.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         108.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/smem data value: 0x10111213 [ABM_0KAY]         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/smem data value: 0x10111213 [ABM_0KAY]         111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm_demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm_demo_tlm_inst/mem data value: 0x1111111 [ABM_0KAY]         I112.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_t                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| 103.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [ [AFM_OKAY]         104.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/aHB_AMBA/default_slave data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/aHB_AMBA/default_slave data value: no value         106.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         108.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         110.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_111.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000105c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_112.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         112.5: /demo_tl                                                                                                                                                                                                                                                                                                                                                                                                                                 | /demo_tlm/demo_tlm_inst/AHB_AMBA/Transfer_Trace                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| 103.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/mem data value: 0xffffffff [AEM_OKAY]         104.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         105.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         106.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         108.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         108.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_III.2.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x00000105c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slav                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102.5: /demo tlm/demo tlm inst/sw read addr: 0x0000102c;                                                                                                                                                                                                  | /demo tlm/demo tlm inst/mem data value: 0xffffffff [ABM 0KAY]                                        |              |  |  |

| 105.5: /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_106.5: /demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_107.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_109.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_110.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tl                                | 103.5: /demo_tlm/demo_tlm_inst/controller idle                                                                                                                                                                                                            | ; /demo_tlm/demo_tlm_inst/mem_data_value: 0xffffffff [ABM_                                           |              |  |  |

| 107.5: /demo_tlm/inst/controller idle       ; /demo_tlm/inst/AHB_AMBA/default_slave data value: no value         108.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x00001028; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_109.5:/demo_tlm/demo_tlm_inst/sw data value: 0x0011123         109.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/sw data value: 0x0011123       [ABM_0KAY]         110.5: /demo_tlm/demo_tlm_inst/controller idle       ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm_/demo_tlm_inst/AHB_AMBA/default_slave data value: no value       [ABM_111.5: /demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm_inst/mem_data value: 0x1111111         Clear       Close         desorptioner       © Licenses @ Servers @ Sessions `Support ? Tools       Dac User 71       @ Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value<br>105.5: /demo_tlm/demo_tlm_inst/sw read addr: 0x00001028; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value  ABM |                                                                                                      |              |  |  |

| 108.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x00001028; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_109.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_110.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_111.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_112.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: no value [ABM_112.5: /demo_tlm/demo_tlm_inst/AHB_AMBA/default_slave data value: 0x1111111 [ABM_0KAY]         Image: Ima                                                          | 106.5: /demo_tlm/demo_tlm_inst/controller idle ; /demo_tlm_inst/mem_data_value: 0x00010203 [ABM_0KAY]                                                                                                                                                     |                                                                                                      |              |  |  |

| 110.5: /demo_tlm_inst/controller idle ; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         111.5: /demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         112.5: /demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         112.5: /demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm_inst/AHB_AMBA/default_slave data value: no value         Interview       Interview         Clear       Close         design@neme       Servers         Servers       Sessions         Support       Tools         Dac User 71       Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108.5: /demo tlm/demo tlm inst/sw write addr: 0x00001028; /demo tlm/demo tlm inst/AHB AMBA/default slave data value: no value [ABM                                                                                                                        |                                                                                                      |              |  |  |

| 111.5: /demo_tlm/demo_tlm_inst/sw write addr: 0x0000102c; /demo_tlm/demo_tlm_inst/AHE_AMBA/deFault_slave data value: no value [ABM_112.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm/demo_tlm_inst/mem data value: 0x1111111 [ABM_0KAY]         112.5: /demo_tlm/demo_tlm_inst/local read addr: 0x0000105c; /demo_tlm/demo_tlm_inst/mem data value: 0x1111111 [ABM_0KAY]         Image: transform the state of the state                                                                                     | 109.5: /demo tlm/demo tlm inst/controller idle ; /demo tlm/demo tlm inst/mem data value: 0x10111213 [ABM OKAY]<br>110 5: /demo tlm/demo tlm inst/controller idle ; /demo tlm/demo tlm inst/ATH ANRA/default slave data value                              |                                                                                                      |              |  |  |

| Clear<br>Clear<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close<br>Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111.5: /demo tlm/demo tlm inst/sw write addr: 0x0000102c; /demo tlm/demo tlm inst/AHB AMBA/default slave data value: no value [ABM]                                                                                                                       |                                                                                                      |              |  |  |

| Clear Close  | 112.5: /demo_tim/demo_tim_inst/local read addr: uxuuuuuuusc                                                                                                                                                                                               | ;; /demo_tim/demo_tim_inst/mem data value: UXIIIIIII [ABM_UKAY]                                      |              |  |  |

| designsphere & Licenses Servers Sessions Support Tools Dac User 71 20 Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           |                                                                                                      | •            |  |  |

| designsphere & Licenses Sessions Support Tools Dac User 71 20 Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chara I                                                                                                                                                                                                                                                   |                                                                                                      |              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                           |                                                                                                      |              |  |  |

| 🙀 Start 🖉 DSA desktop started - Micr 🖉 DesignSphere - Micro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | designsphere 🍽 Licenses 📓 Servers 🗃 Sessions 🌂 Support 👘                                                                                                                                                                                                  | Tools Dac User 71 20                                                                                 | Disconnect   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Start 🖉 DSA desktop started - Micr 🍘 DesignSphere - Micro                                                                                                                                                                                                 |                                                                                                      | ₩♀₩ 23:06    |  |  |

Multimedia SoC Design

### TL Modeling System performance analysis

Multimedia SoC Design

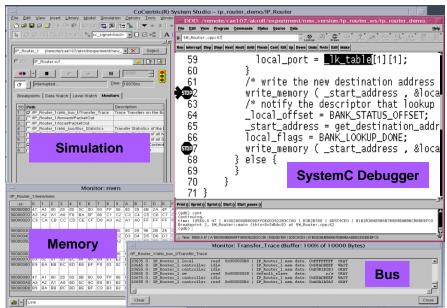

# Early Software Verification

SW running on workstation with

annotated time or HW synchronized

#### **SW development**

- Algorithm

- Target indep. code

- Target code

Early SW Verification significantly shortens Integration and Validation

# **TL Modeling - Benefits**

### High Performance

- potential for 100x speed over RTL

- Early architectural closure

- □ A platform for software developers to write code

- Model for early system analysis

- Reuse of functional test bench

- Architecture Verification

- □ Analysis of cache/memory architecture

- □ System latency

- TL model library

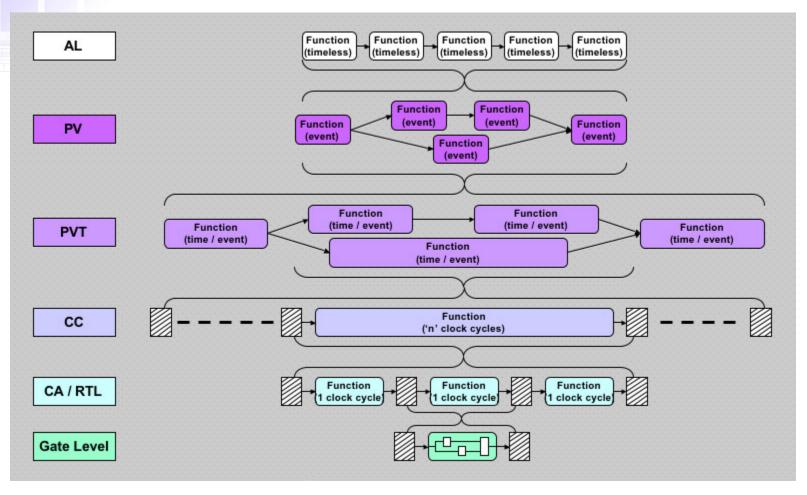

### More Details about More General Transaction-Level Modeling

#### Abstractions

- □ Algorithmic level (AL)

- Architecture/implementation independent

- □ Programmers View (PV)

- Bit-true representation of the HW, register accurate, no detailed timing

- Programmer View + Timing (PVT)

- Same as PV plus detailed timing and synchronization (cycle approximate in most cases)

- □ Cycle Accurate (CA)

- Clocked abstraction, interfaces and transactions

- 🗆 RTL

- Clocked abstraction, actual chip signals

Multimedia SoC Design

### Transaction-Level Modeling Abstractions

Multimedia SoC Design

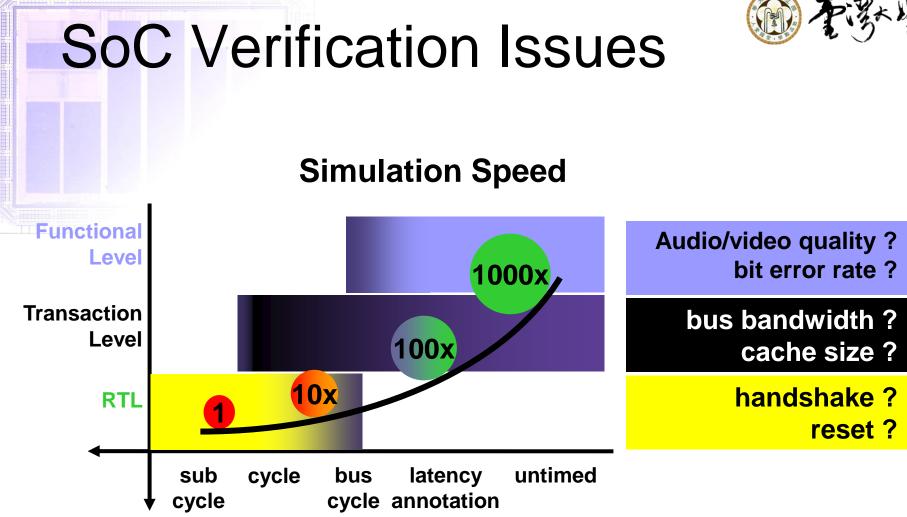

# Register Transfer Level Modeling

| Functionality  | Yes          |

|----------------|--------------|

| Cycle Accuracy | Yes          |

| Timing         | Yes          |

| Pin Accuracy   | Yes          |

| Communication  | Shared       |

| Channel        | Signals only |

| Parameters     | Yes          |

## **RT Level Models**

#### Functionality of the device

#### All signal interactions with the bus

- Databus

- Address bus

- Control

- signal characteristics (active high/low)

- reset characteristics

- bus responses

- arbitration protocols

Accurate timing information of signals

## **RTL - Benefits**

- Well understood semantics

- Popular languages

- □ Verilog, VHDL

- □ SystemC (not primarily targeted at RTL)

- Synthesize-ability

- well defined synthesis tools and methodology

- Analysis capabilities

- accurate timing analysis and verification tools

- RTL models can be plugged into TL models with adaptors

Multimedia SoC Design

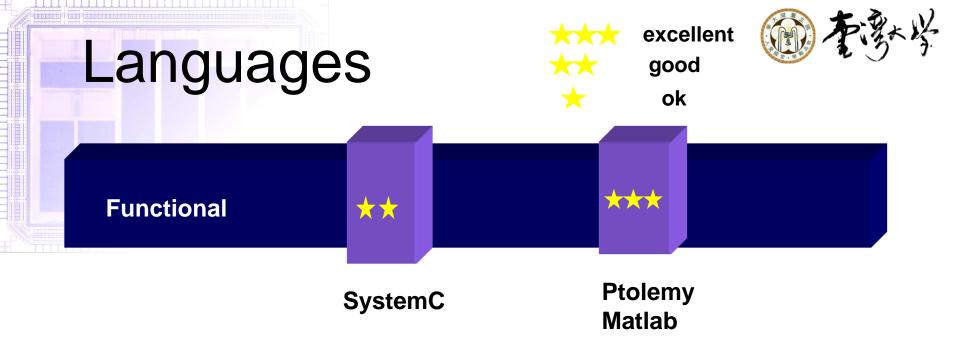

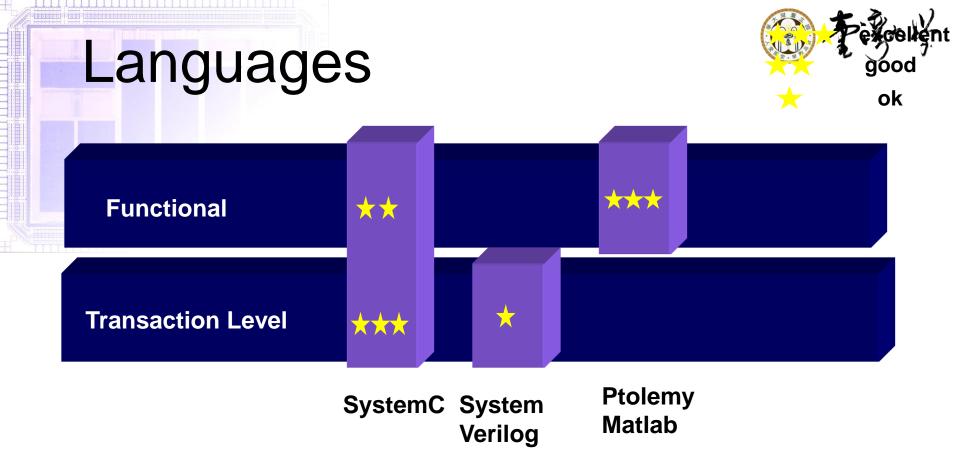

VHDL Verilog

Multimedia SoC Design

SystemC System Verilog Shao-Yi Chien Ptolemy Matlab

#### System-C or SystemVerilog?

#### System-C

- A library

- □ Built on C++

SystemVerilog

- Can be support by your C compiler

- For advanced tools, will be supported by Cadence, Coware, MentorGrahics, Synopsys, …

- SystemVerilog

- □ A new language

- Next generation of Verilog

- Supported by your Verilog simulator and synthesizer

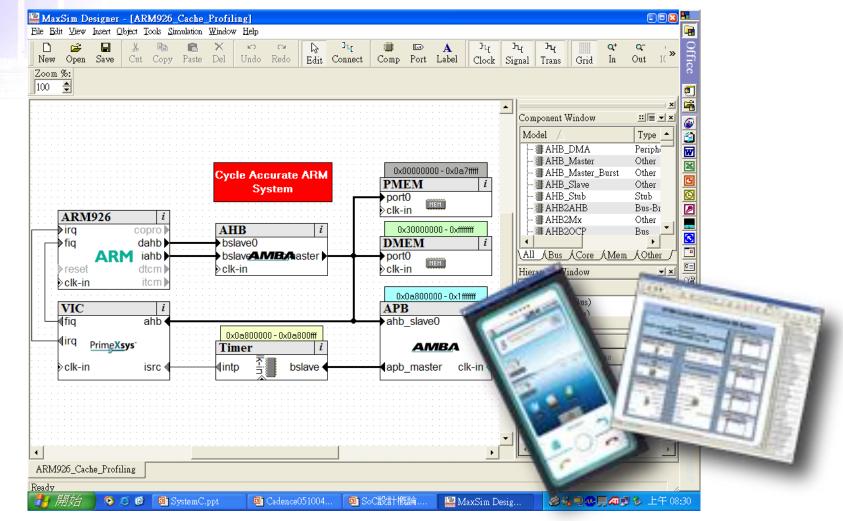

# SystemC

http://www.systemc.org

- 1997: Scenic Design Framework (Synopsys, UC Irvine, DAC'97)

- 1999: Open SystemC Initiative (Synopsys, CoWare)

- 1999: SystemC v0.9, C++ class library

- 2000: SystemC 1.0

- 2000: Cadence joins OSCI

- 2001: Mentor Graphics joins OSCI

- 2001: SystemC Release 2.0

- □ higher levels of abstraction

- □ interfaces, channels, ports